PRÁCTICA EMPRESARIAL EN LA UEE BIOINGENIERÍA DE LA FUNDACIÓN CARDIOVASCULAR DE COLOMBIA: DISEÑO, OPTIMIZACIÓN E IMPLEMENTACIÓN DEL SISTEMA SOFTWARE-HARDWARE E INTERFAZ GRÁFICA DE INTERACCIÓN CON EL USUARIO DE UN DISPOSITIVO DE MONITORIZACIÓN VITAL

JOSE MANUEL VELANDIA ROJAS

UNIVERSIDAD PONTIFICIA BOLIVARIANA - SECCIONAL BUCARAMANGA FACULTAD DE INGENIERÍA ELECTRÓNICA ESCUELA DE INGENIERÍAS BUCARAMANGA 2014 PRÁCTICA EMPRESARIAL EN LA UEE BIOINGENIERÍA DE LA FUNDACIÓN CARDIOVASCULAR DE COLOMBIA: DISEÑO, OPTIMIZACIÓN E IMPLEMENTACIÓN DEL SISTEMA SOFTWARE-HARDWARE E INTERFAZ GRÁFICA DE INTERACCIÓN CON EL USUARIO DE UN DISPOSITIVO DE MONITORIZACIÓN VITAL

JOSE MANUEL VELANDIA ROJAS

LIBRO FINAL DE PRÁCTICA EMPRESARIAL PARA OPTAR POR EL TITULO DE INGENIERO ELECTRÓNICO

Supervisor académico: MSc. CLAUDIA LEONOR RUEDA GUZMÁN

Supervisor empresarial: ING. LEONARDO ANDRÉS RODRIGUEZ SALAZAR

UNIVERSIDAD PONTIFICIA BOLIVARIANA - SECCIONAL BUCARAMANGA FACULTAD DE INGENIERÍA ELECTRÓNICA ESCUELA DE INGENIERÍAS BUCARAMANGA 2014

# **CONTENIDO**

|                                                                                    | Pág. |

|------------------------------------------------------------------------------------|------|

| INTRODUCCIÓN                                                                       | 16   |

| 1. ESTUDIO INICIAL Y METODOLOGIA DE TRABAJO                                        | 21   |

| 1.1 COMPRESIÓN DE LOS SISTEMAS PREVIAMENTE DESARROLLADOS                           |      |

| 1.1.1 Extracción de la dinámica base                                               | 22   |

| 1.1.2 Uso de propiedades intelectuales (IP)                                        | 25   |

| 1.1.3 Cuestionamientos iniciales                                                   |      |

| 1.2 INVESTIGACIÓN Y FAMILIARIZACIÓN CON EL ÁREA DE TRABAJO                         | 26   |

| 1.2.1 Problemas que impulsaron la investigación                                    | 26   |

| 1.2.2 Evidencia de la investigación.                                               |      |

| 1.2.3 Contacto con el personal médico.                                             |      |

| 1.3 ESTUDIO DE TÉCNICAS DE DISEÑO Y DESARROLLO                                     |      |

| 1.3.1 Técnicas de desarrollo hardware.                                             | 31   |

| 1.3.1.2 Lenguajes de descripción hardware                                          | 32   |

| 1.3.2 Técnicas de desarrollo software                                              |      |

| 1.3.2.1 Problemática del desarrollo software.                                      | 33   |

| 1.3.2.2 Administración de versiones software.                                      | 34   |

| 1.3.2.2.1 La realidad sobre "SourceTree"                                           | 35   |

| 1.3.2.2.2 Comprensión de la plataforma "SourceTree"                                | 36   |

| 1.3.2.2.3 Detalles y opcionalidades finales en cuanto a la administración software |      |

| 1.3.2.3 Solución de la problemática en base a la administración de ventanas        | 38   |

| 1.3.2.4 Cursos de programación en línea.                                           | 38   |

| 1.3.2.5 Cuestionamientos previos al desarrollo (Metodología software)              | 39   |

| 1.3.2.6 Abstracción de la dinámica software.                                       | 40   |

| 1.3.2.6.1 Comparativa de la dinámica entre códigos software                        | 41   |

| 1.3.2.6.2 Dinámica del código C++ (Objetos)                                        | 42   |

| 2. DESARROLLO FORMAL SOBRE LOS SISTEMAS DEFINIDOS                                  | 44   |

| 2.1 INCURSIÓN EN LOS ENTORNOS DE DESARROLLO                                        | 44   |

| 2.1.1 Entornos de desarrollo hardware sobre FPGAs                                  | 44   |

| 2.1.1.1 Entorno de compilación y desarrollo de la lógica programable de la FPGA    | 44   |

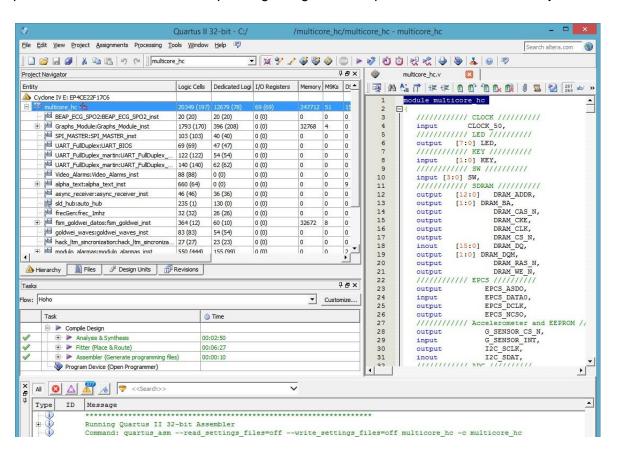

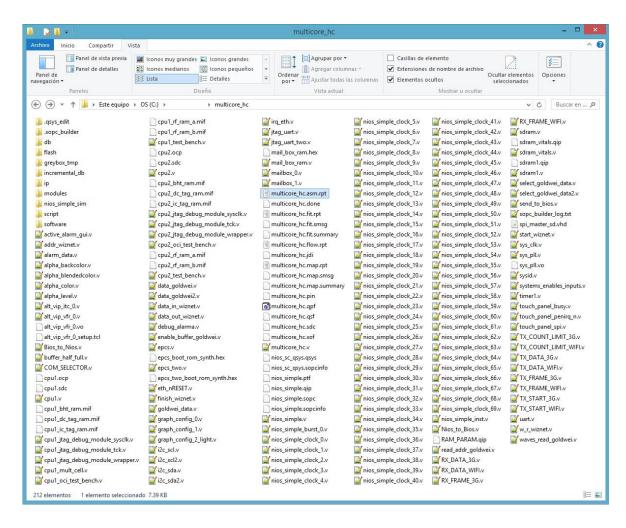

| 2.1.1.1.1 Compilación y abstracción del sistema hardware del MSV                   | 46   |

| 2.1.1.2 Entornos de desarrollo hardware de sistemas integrados                     | 49   |

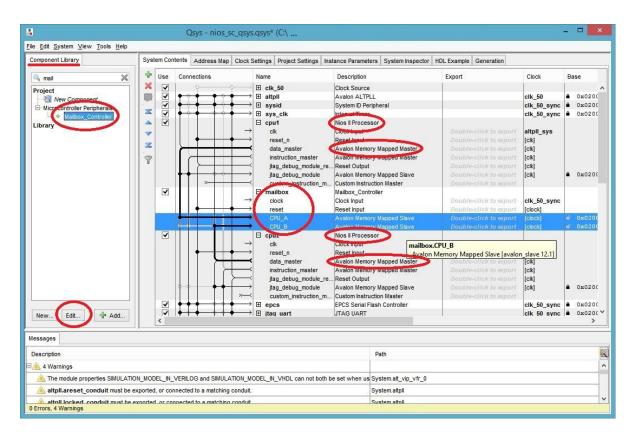

| 2.1.1.2.1 Desarrollo sobre entornos de sistemas integrados (Qsys)                  | 51   |

| 2.1.1.2.1.1 Organización del espacio de trabajo.                                   | 51   |

| 2.1.1.2.1.2 Armado del sistema                                                     |      |

| 2.1.1.2.1.3 Interconexión explicita de los sistemas maestro-esclavo                | 55   |

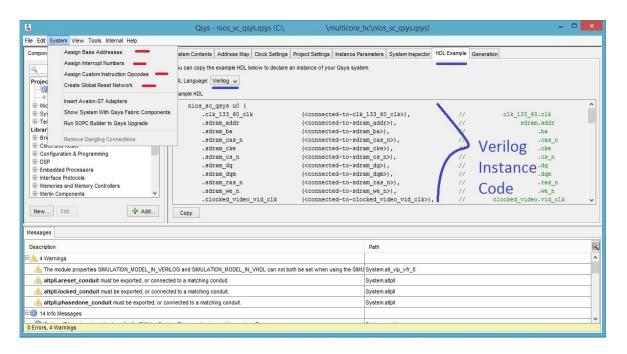

| 2.1.1.2.1.4 Revisiones, instanciación y compilación del chip final                              | 57  |

|-------------------------------------------------------------------------------------------------|-----|

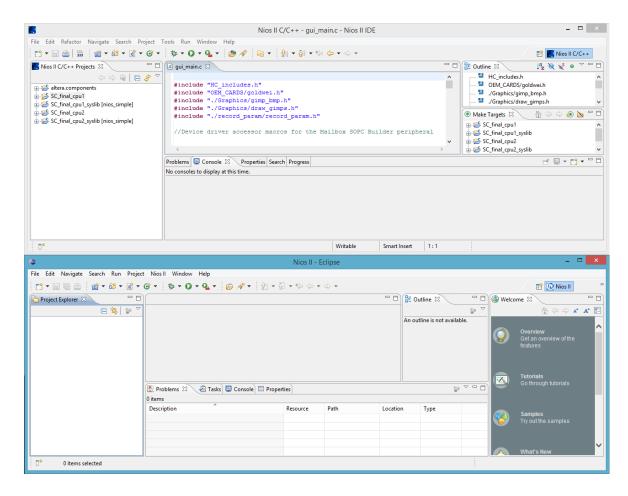

| 2.1.2 Introducción a entornos de desarrollo software                                            | 60  |

| 2.1.3 Edición software alejada de los entornos dispuestos                                       | 62  |

| 2.2 ELIGIENDO EL SISTEMA OPERATIVO DEL PROYECTO SOFTWARE                                        | 62  |

| 2.2.1 Adquiriendo derechos sobre las librerías del sistema operativo disponible                 | 63  |

| 2.3 SOLUCIÓN DE ERRORES DE DESCRIPCIÓN HARDWARE                                                 | 63  |

| 2.4 COMPRENSIÓN Y CREACIÓN DE COMPONENTES SOBRE EL ENTORNO Q                                    | SYS |

|                                                                                                 | 67  |

| 2.4.1 Presentación del componente.                                                              |     |

| 2.4.2 Creación y edición del componente.                                                        |     |

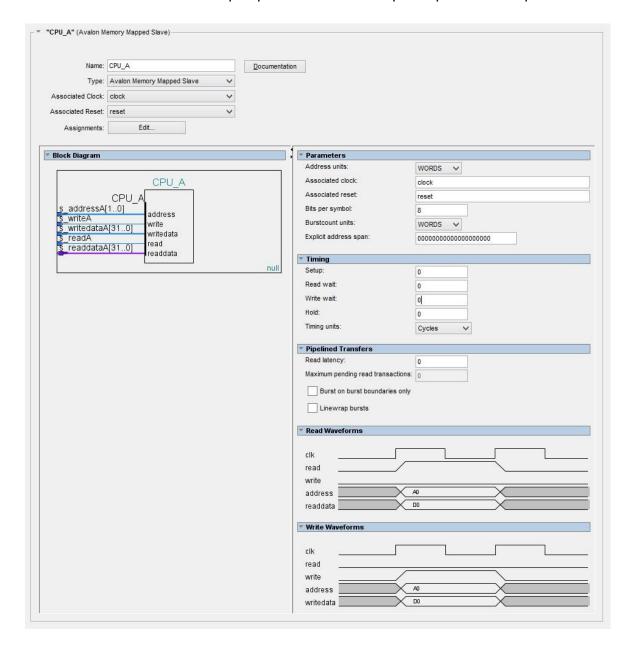

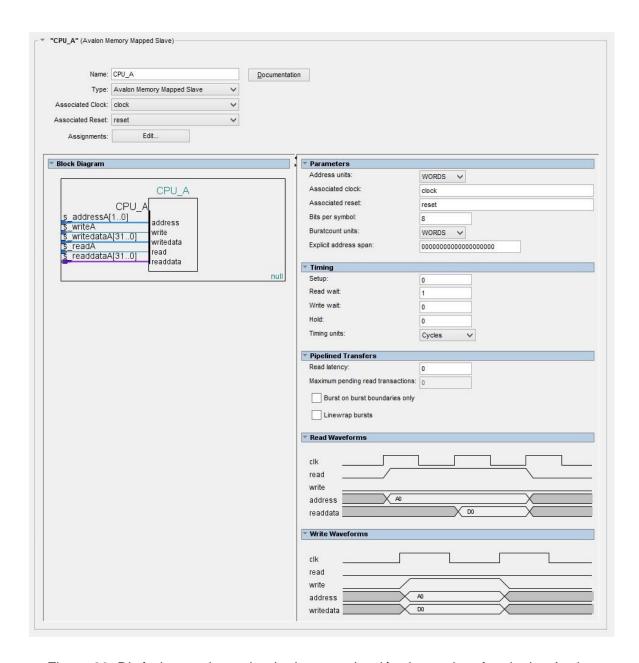

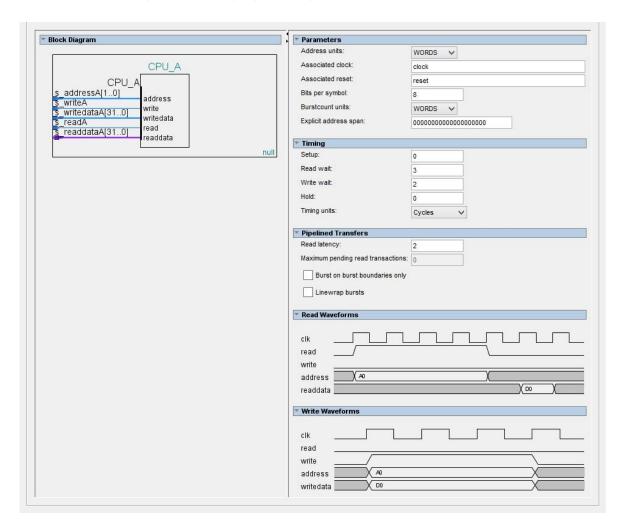

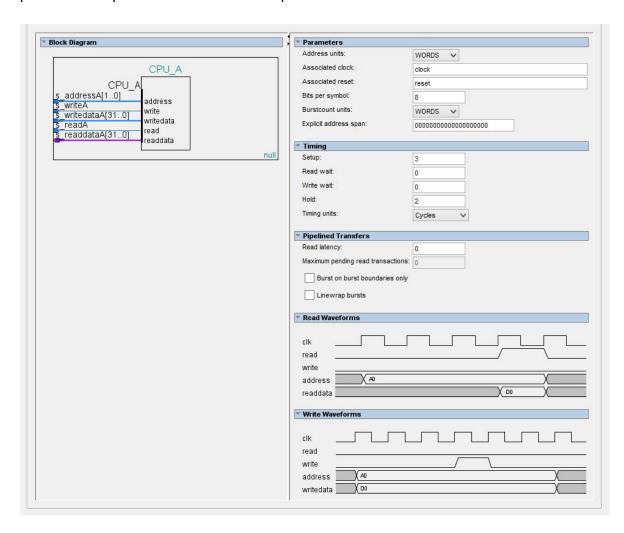

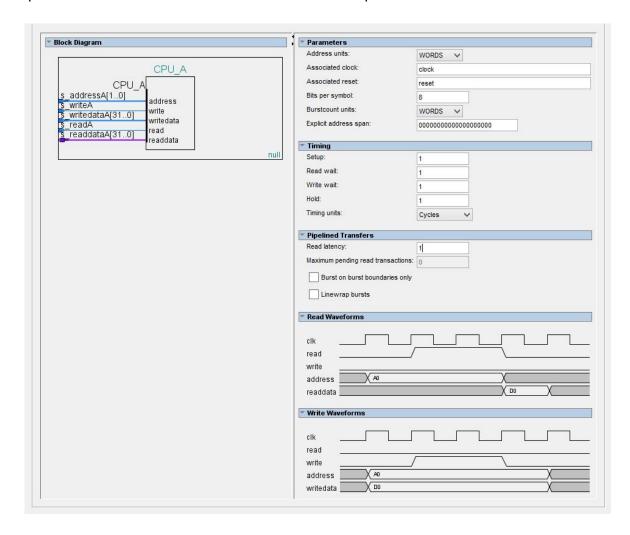

| 2.4.3 Temporización del estándar de comunicación "Avalon Memory Mapped"                         | 74  |

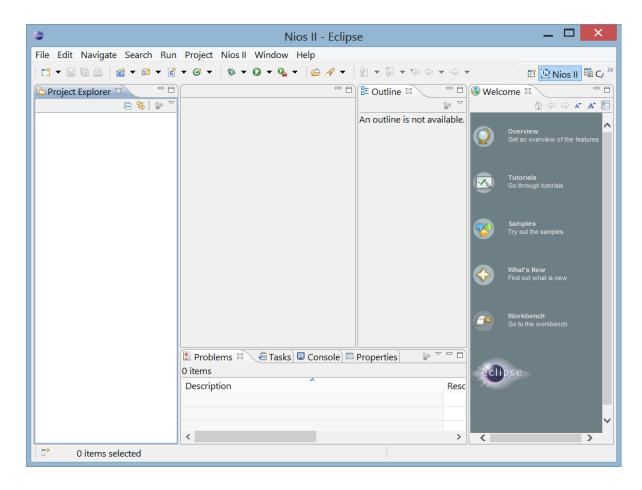

| 2.5 DESARROLLO SOFTWARE SOBRE EL ENTORNO NIOS II ECLIPSE                                        | 82  |

| 2.5.1 Presentación del entorno.                                                                 | 82  |

| 2.5.2 Creación y configuración de proyectos.                                                    | 86  |

| 2.5.2.1 Comprensión y uso de la distribución de memoria hardware prevista                       | 92  |

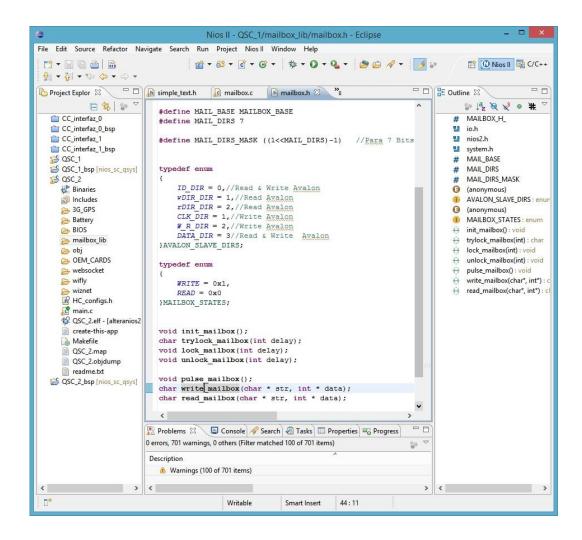

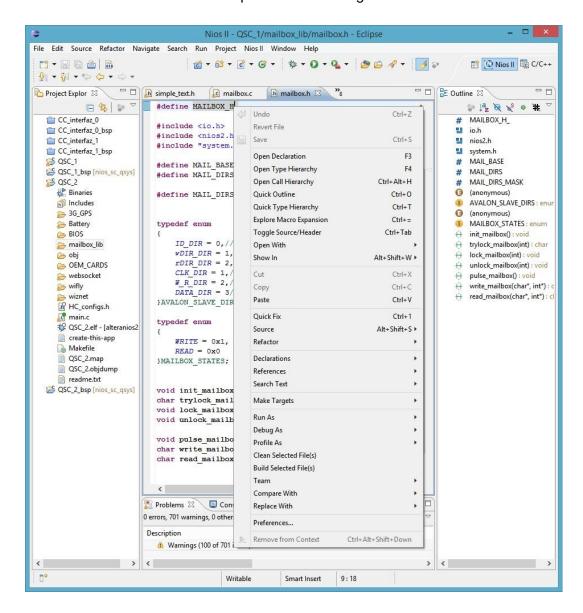

| 2.5.3 Programación y verificación de la lógica software embebida en los proyectos               | 93  |

| 2.6 EDICIÓN SOFTWARE SOBRE LA HERRAMIENTA QT CREATOR                                            |     |

| 2.6.1 Presentación de la herramienta.                                                           | 97  |

| 2.6.2 Edición software de las librerías controladoras.                                          | 98  |

| 2.7 COMPRENSIÓN SOFTWARE DE LA DINÁMICA DEL SISTEMA OPERATIVO                                   | 100 |

| 2.7.1 Uso del sistema operativo uC/OS II como herramienta útil en la ejecución de               |     |

| tareas software                                                                                 |     |

| 2.7.2 Dinámica software de una GUI junto al sistema operativo uC/OS II y leng                   |     |

| orientado a objetos (C++).                                                                      |     |

| 2.7.3 Dinámica software de redes junto al sistema operativo uC/OS II y lenguaje orien           |     |

| a objetos (C++).                                                                                |     |

| 2.7.4 Avances de desarrollo software en cuanto a interfaz gráfica de usuario (GUI)              |     |

| 2.8 GESTIÓN DE ADQUISICIÓN VÍA E-MAIL PARA COMPRA DE DIRECCIO FÍSICAS DE RED O MAC IEEE STD 802 |     |

| 2.9 "BIOS" LA IMPORTANCIA DEL CONTROL A BAJO NIVEL: AUTOMATIZACIÓN FI                           |     |

| DEL DISPOSITIVO                                                                                 |     |

| 2.9.1 Concepto de BIOS.                                                                         |     |

| 2.9.2 Dinámica BIOS sobre la lógica del equipo médico                                           |     |

| 2.9.3 Estructura física y de conexión BIOS sobre el hardware que abarca el eq                   |     |

| médico                                                                                          |     |

| 2.9.4 Lógica software de BIOS como Firmware base del equipo médico                              |     |

| 2.9.4.1 Entorno Atmel Studio como herramienta de desarrollo software                            |     |

| 2.9.4.2 Estructura de proyectos software en el entorno Atmel Studio                             |     |

| 2.9.4.3 Programación de la compilación software sobre el entorno Atmel Studio                   |     |

| 2.10 DEPURACIÓN Y TRABAJO CONTINUO EN LA CORRECCIÓN DE ERRORES .                                |     |

|        |          |       |             |     |       | <br>DISPOSITIVO | <br>    |

|--------|----------|-------|-------------|-----|-------|-----------------|---------|

| INTER/ | ACCIÓN C | CON L | _A INTERFAZ | GR/ | ÁFICA | <br>            | <br>125 |

| 3. APO | RTE AL C | ONO   | CIMIENTO    |     |       | <br>            | <br>127 |

| 4. CON | NCLUSION | NES   |             |     |       | <br>            | <br>129 |

| BIBLIO | GRAFÍA   |       |             |     |       | <br>            | <br>131 |

# **LISTA DE FIGURAS**

|                  | _ |   |

|------------------|---|---|

| $\boldsymbol{r}$ | а | a |

|                  | u | ч |

| Figura 1. Sistemas externos del MSV e interacción con el mundo físico                                                 |

|-----------------------------------------------------------------------------------------------------------------------|

| Figura 2. Esquema de correlación de las tareas, respecto a la tarjeta de procesamiento principal                      |

| Figura 3. Pruebas en video - Verificación de alarmas y representación de valores estáticos en monitor comercial       |

| Figura 4. Pruebas en video - Verificación de límites de alarmas y modos gráficos de las ondas vitales                 |

| Figura 5. Pruebas en video - Verificación de sonidos, pausa de alarmas, iconografía de interfaz e iconografía externa |

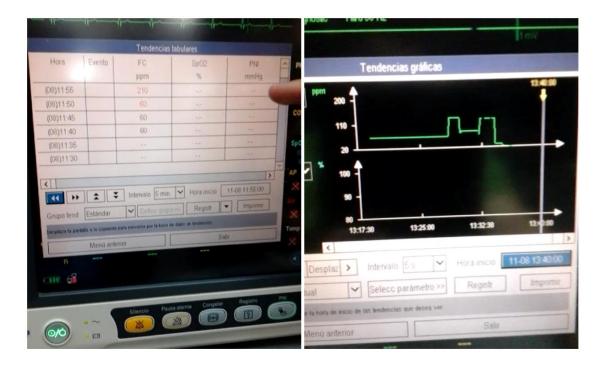

| Figura 6. Pruebas en video - Sistema de tendencia gráfica y tabular de datos estáticos guardado de eventos            |

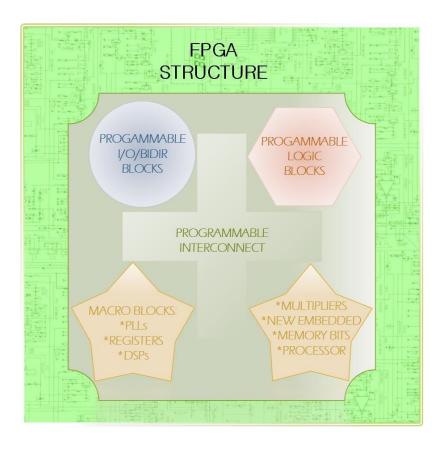

| Figura 7. Lógica interna de las FPGAs                                                                                 |

| Figura 8. Esencia del sistema de descripción hardware "Verilog"                                                       |

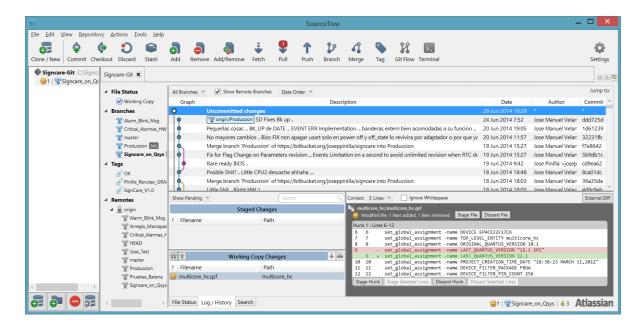

| Figura 9. Estructura de la administración de versiones                                                                |

| Figura 10. SourceTree como aplicación dentro del sistema operativo Windows 8 37                                       |

| Figura 11. Ciclo de abstracción software sobre sistemas de procesamiento integrado 47                                 |

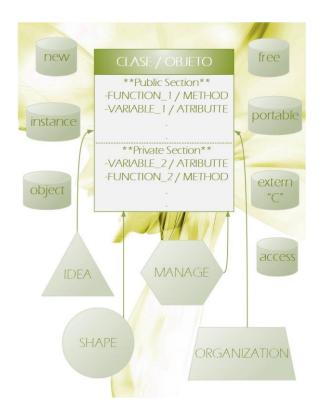

| Figura 12. Estructura de la clase y conceptos propios del código C++                                                  |

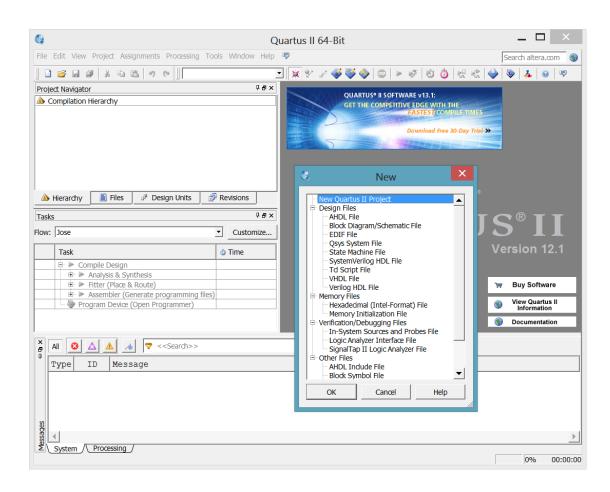

| Figura 13. Quartus II, descriptor de interfaces de tipo hardware                                                      |

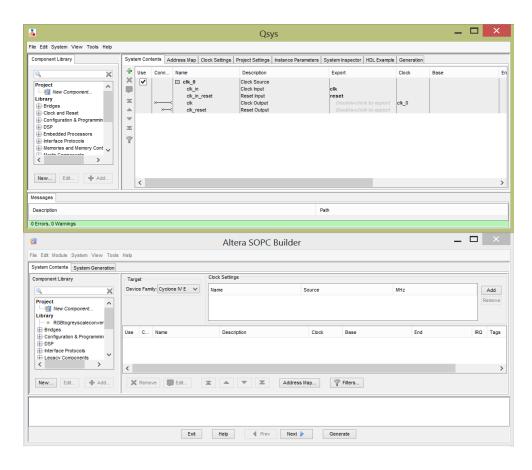

| Figura 14. Entornos de desarrollo hardware Qsys y SOPC Builder                                                        |

| Figura 15. Ejemplo de desarrollo sobre la plataforma Quartus                                                          |

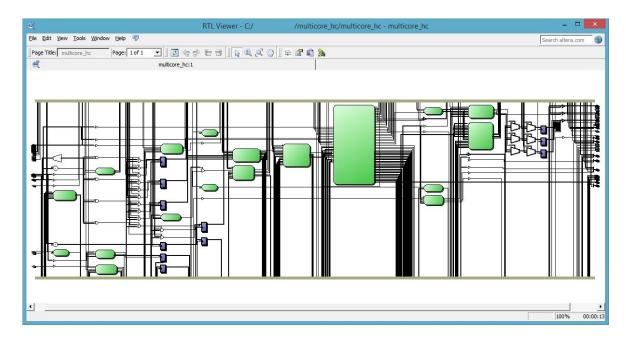

| Figura 16. Sistema hardware base del equipo de monitorización en representación RTL 48                                |

| Figura 17. Diseño y desarrollo modular de sistemas embebidos basados en tecnología FPGA                               |

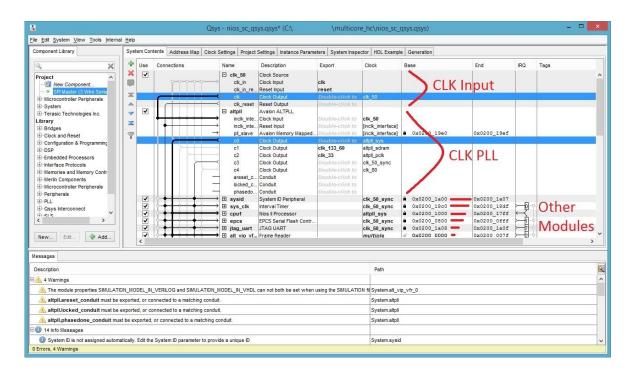

| Figura 18. Adecuación del entorno Qsys, detalles base de la herramienta                                               |

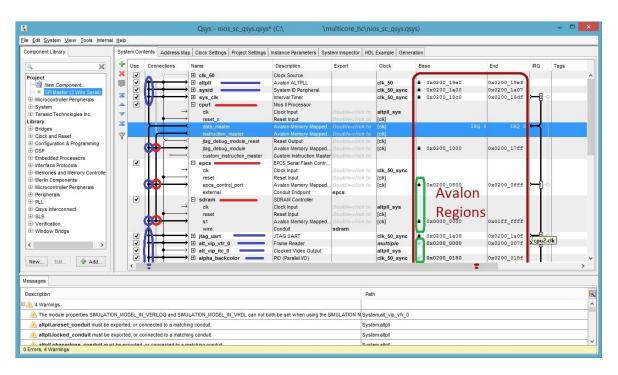

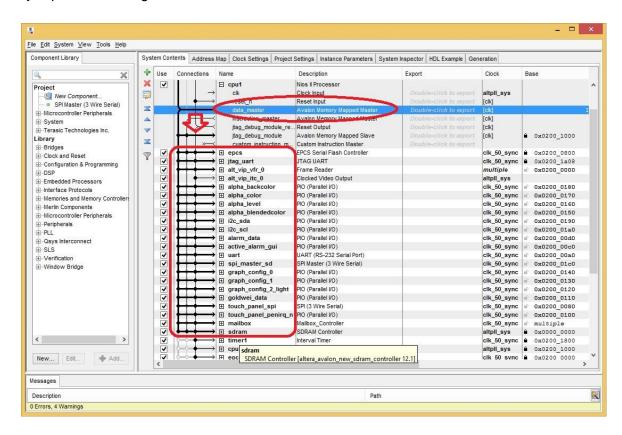

| Figura 19. Descripción gráfica "Qsys" de un chip de desarrollo sobre FPGA 54                                          |

| Figura 20. Estructura de conexión sobre el procesador Nios II                                                         |

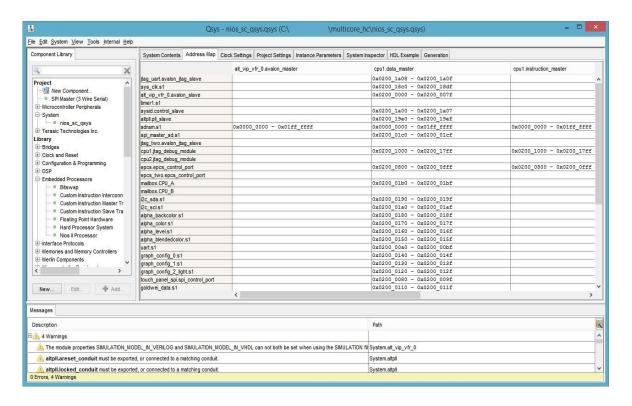

| Figura 21. Mapa de direcciones relativas Avalon 57                                                                    |

| Figura 22. Opciones funcionales de edición e Instanciación final sobre el entorno Qsys . 58                           |

| Figura 23. Generación forzosa de archivos por parte del entorno SOPC Builder 60                                       |

| Figura 24. Entornos "Java" de desarrollo software, sobre procesadores (Nios II) basados                               |

| en tecnología de la corporación Altera6                                                                               |

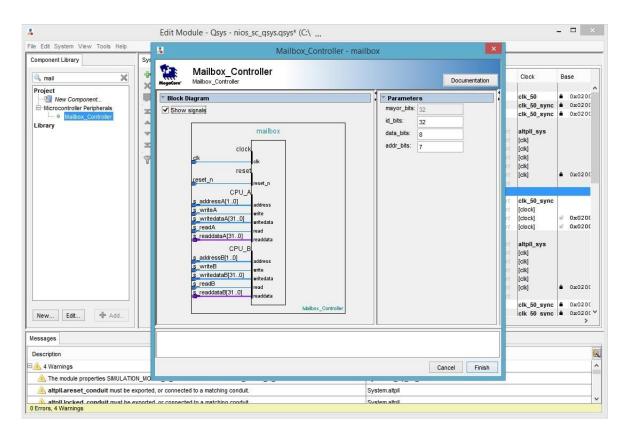

| Figura 25. Módulo "mailbox" e interconexión de procesadores sobre el entorno Qsys 68                                  |

| Figura 26. Estructura de comunicación "mailbox" sobre el entorno Qsys 69                                              |

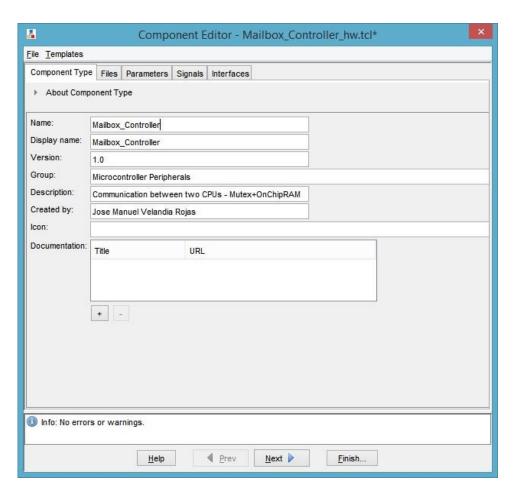

| Figura 27. Pestaña de descripción básica del módulo "mailbox" sobre la herramienta de edición del entorno Qsys        |

| Figura 28. Pestaña de archivos de descripción del módulo "mailbox" sobre la herramienta de edición del entorno Qsys                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

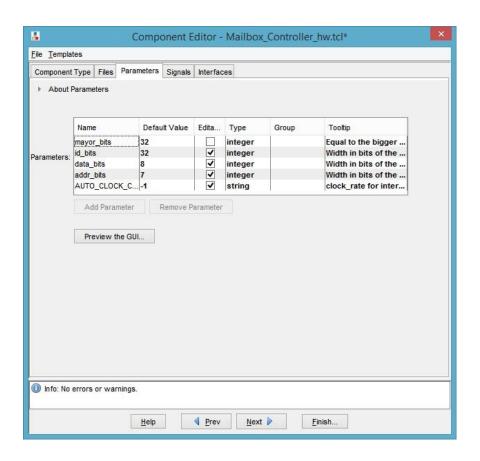

| Figura 29. Pestaña de parámetros del módulo "mailbox" sobre la herramienta de edición del entorno Qsys                                                                                                    |

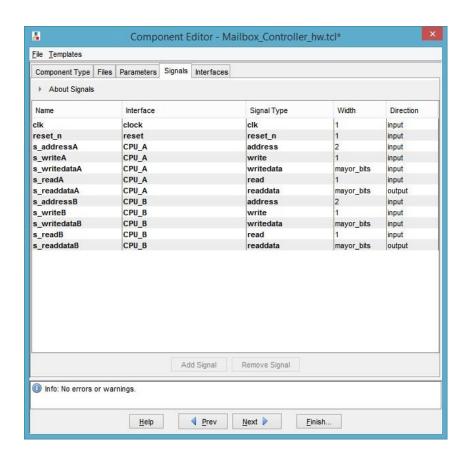

| Figura 30. Pestaña de señales hardware del módulo "mailbox" sobre la herramienta de edición del entorno Qsys                                                                                              |

| Figura 31. Pestaña de Interfaces del módulo "mailbox" sobre la herramienta de edición del entorno Qsys                                                                                                    |

| Figura 32. Dinámica modificada de comunicación de una interfaz de tipo Avalon Memory Mapped - Slave                                                                                                       |

| Figura 33. Dinámica predeterminada de comunicación de una interfaz de tipo Avalon Memory Mapped - Slave                                                                                                   |

| Figura 34. Timing 1 - Configuración aleatoria de la comunicación de una interfaz de tipo Avalon Memory Mapped - Slave                                                                                     |

| Figura 35. Timing 2 - Configuración aleatoria de la comunicación de una interfaz de tipo Avalon Memory Mapped - Slave                                                                                     |

| Figura 36. Timing 3 - Configuración aleatoria de la comunicación de una interfaz de tipo Avalon Memory Mapped - Slave                                                                                     |

| Figura 37. Entorno gráfico de desarrollo Nios II Eclipse                                                                                                                                                  |

| Figura 38. Entorno gráfico de desarrollo Nios II Eclipse – Edición de proyectos 84                                                                                                                        |

| Figura 39. Entorno gráfico de desarrollo Nios II Eclipse – Opciones de búsqueda y edición.                                                                                                                |

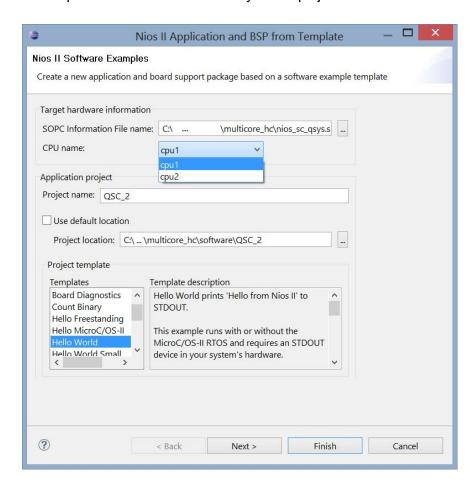

| Figura 40. Entorno gráfico de desarrollo Nios II Eclipse – Creación de proyectos software en base a descripción hardware                                                                                  |

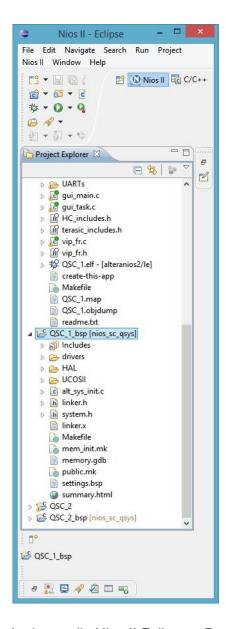

| Figura 41. Entorno gráfico de desarrollo Nios II Eclipse – Proyecto software: carpeta de desarrollo y carpeta BSP básica de funcionalidades y definiciones propias del sistema que envuelve al procesador |

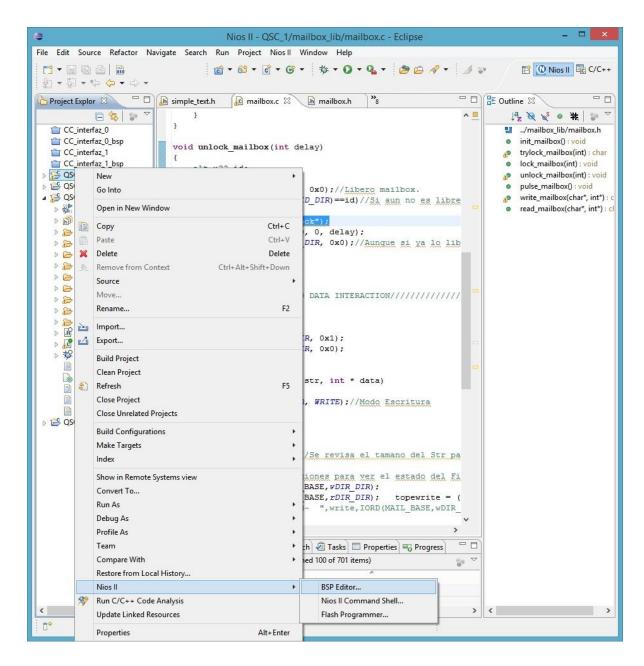

| Figura 42. Entorno gráfico de desarrollo Nios II Eclipse – Edición final de las características de ejecución software a través de la herramienta de edición BSP                                           |

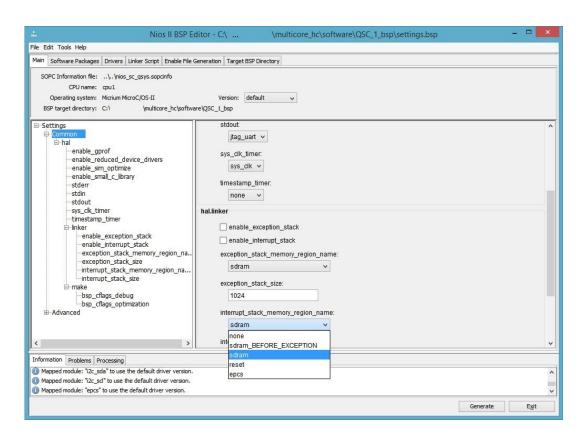

| Figura 43. Entorno gráfico de desarrollo Nios II Eclipse – Edición BSP, pestaña principal de configuración básica                                                                                         |

| Figura 44. Entorno gráfico de desarrollo Nios II Eclipse – Edición BSP, pestaña de descripción de las diferentes regiones memoria del procesador                                                          |

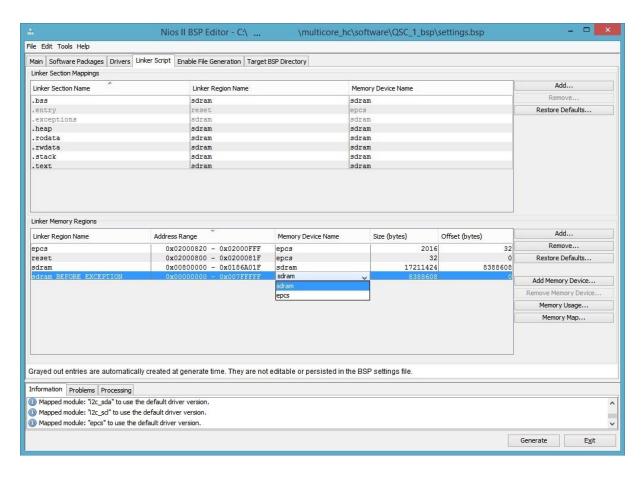

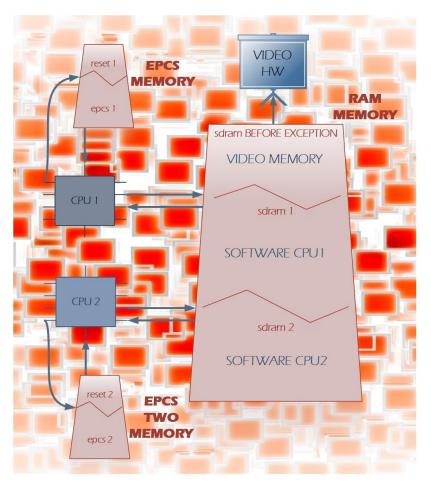

| Figura 45. Repartición de las diferentes regiones de memoria existentes para el uso compartido entre los procesadores y el hardware de video dedicado                                                     |

| Figura 46. Interfaz gráfica de programación software de los procesadores Nios II 94                                                                                                                       |

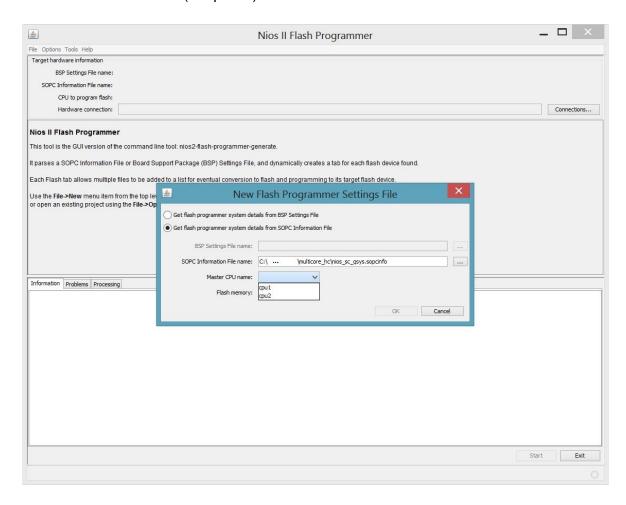

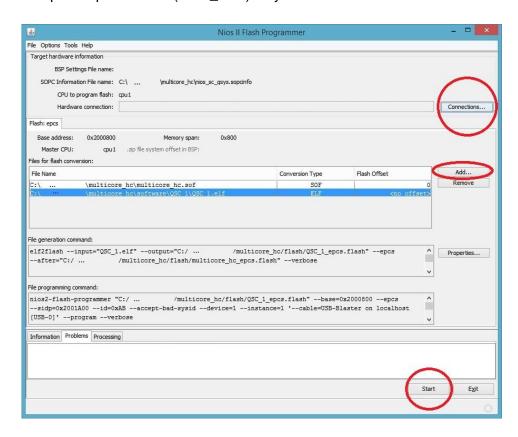

| Figura 47. Ejemplo de programación no volátil sobre la herramienta "Nios II Flash Programmer"                                                                                                             |

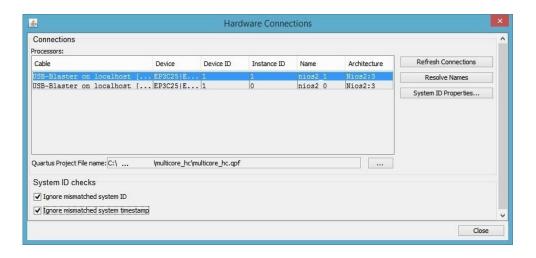

| Figura 48. Verificación de la existencia de los procesadores hardware a programar de                                                                                                                      |

| manera software dentro de la FPGA96                                                                                                                                                                       |

| Figura 49. Consola de comandos "Nios II command Shell"                                                                                                                                                    |

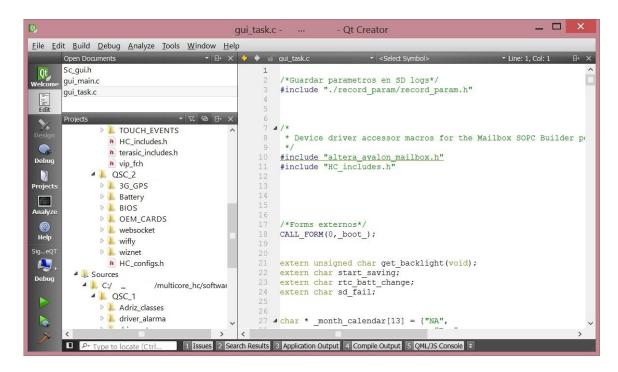

| Figura 50. Herramienta de desarrollo software "QT Creator"                                                                                                                                                |

| Figura 51. Parte del código fuente de la librería controladora sugerida para el módulo mailbox "mailbox.c"                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

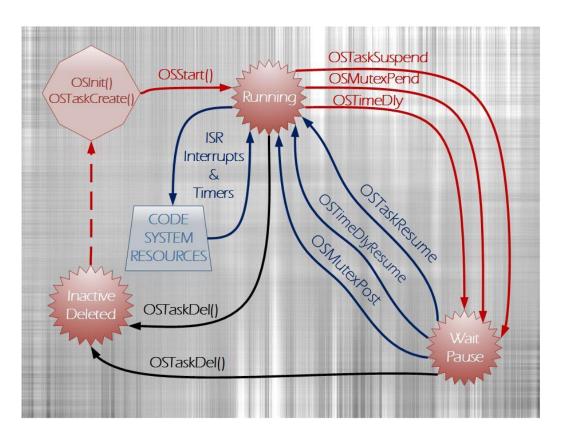

| Figura 52. Dinámica de operación del sistema operativo uC/OS II de la compañía Micrium.                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                            |

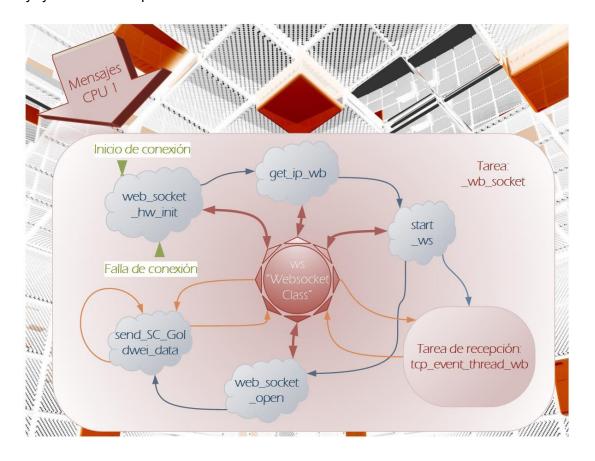

| Figura 53. Dinámica de operación software del primer procesador 103                                                                                                                                                                                                                                                                                                                                                        |

| Figura 54. Dinámica de operación software del primer procesador 104                                                                                                                                                                                                                                                                                                                                                        |

| Figura 55. Dinámica de operación de red sobre el software del segundo procesador 105                                                                                                                                                                                                                                                                                                                                       |

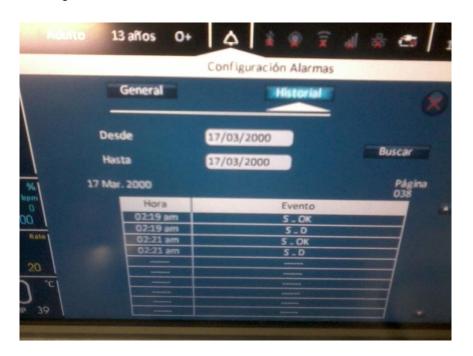

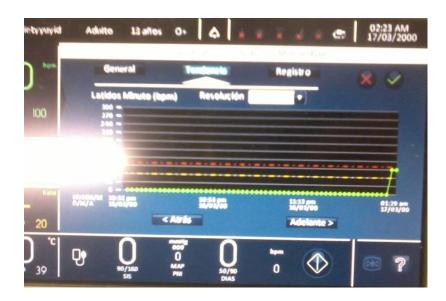

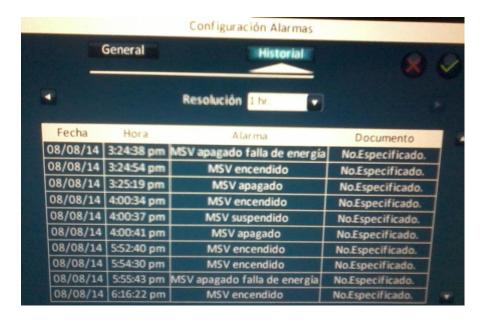

| Figura 56. Antiguo menú de historial de alarmas                                                                                                                                                                                                                                                                                                                                                                            |

| Figura 57. Antiguo menú de tendencias gráficas y representación de las variables                                                                                                                                                                                                                                                                                                                                           |

| estáticas sobre el número cero (0)                                                                                                                                                                                                                                                                                                                                                                                         |

| Figura 58. Antiguo menú técnico del monitor                                                                                                                                                                                                                                                                                                                                                                                |

| Figura 59. Nuevo menú de técnico con calibración de presión del monitor 108                                                                                                                                                                                                                                                                                                                                                |

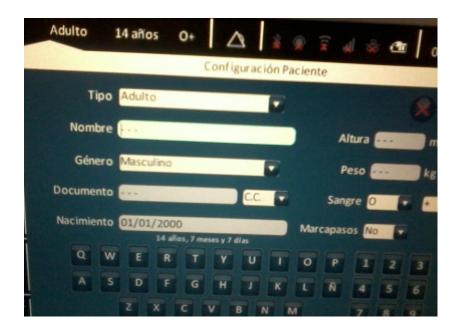

| Figura 60. Nuevo menú de tendencias gráficas con mayor rango de tiempo y representación de las variables estáticas nulas a través del texto "" como sucede con las maritares con mayor rango de tiempo y |

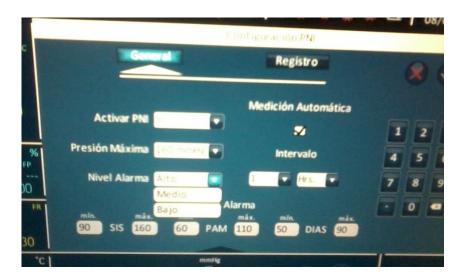

| los monitores comerciales en el mercado.                                                                                                                                                                                                                                                                                                                                                                                   |

| Figura 61. Nuevo menú de historial de alarmas en búsqueda                                                                                                                                                                                                                                                                                                                                                                  |

| Figura 62. Nuevo menú de historial de alarmas final.                                                                                                                                                                                                                                                                                                                                                                       |

| Figura 63. Modificaciones al menú de paciente                                                                                                                                                                                                                                                                                                                                                                              |

| Figura 64. Modificaciones al menú de PANI (Presión Arterial no Invasiva)110                                                                                                                                                                                                                                                                                                                                                |

| Figura 65. Modificaciones a los mensajes de ondas vitales                                                                                                                                                                                                                                                                                                                                                                  |

| Figura 66. Nuevo modo calibración del "Touch" o táctil resistivo                                                                                                                                                                                                                                                                                                                                                           |

| Figura 67. Nuevas técnicas de evasión de errores en memoria SD112                                                                                                                                                                                                                                                                                                                                                          |

| Figura 68. Nuevas técnicas de evasión de errores en cuanto a configuración de edad112                                                                                                                                                                                                                                                                                                                                      |

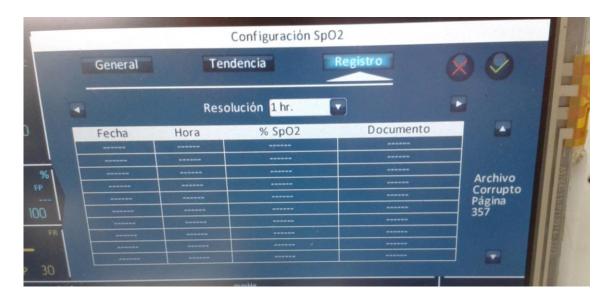

| Figura 69. Nuevas técnicas de evasión de errores de lectura en archivos corruptos113                                                                                                                                                                                                                                                                                                                                       |

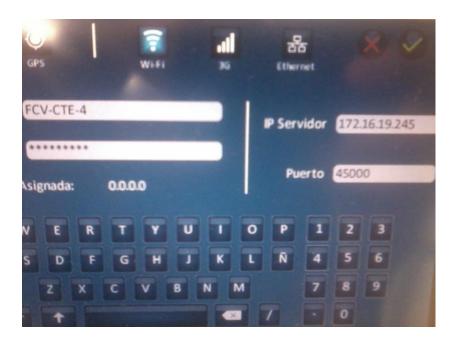

| Figura 70. Creación de los menús de redes inalámbricas con funcionalidad real113                                                                                                                                                                                                                                                                                                                                           |

| Figura 71. Corrección de la funcionalidad de marcapasos de la tarjeta de adquisición114                                                                                                                                                                                                                                                                                                                                    |

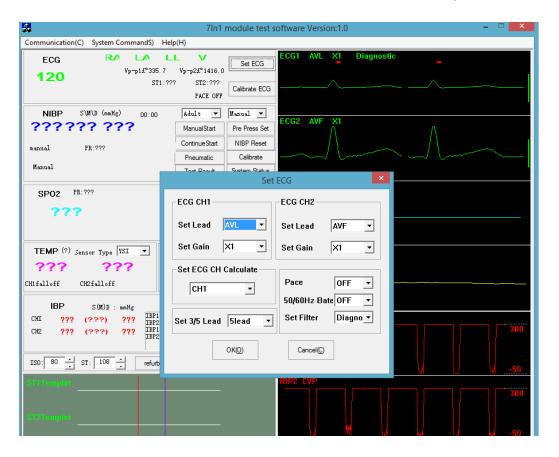

| Figura 72. Variadas verificaciones de orden con ayuda del software interactivo propio de la tarjeta de adquisición vital vía terminal USB-UART114                                                                                                                                                                                                                                                                          |

| Figura 73. Variadas verificaciones de orden con ayuda del comportamiento típico en                                                                                                                                                                                                                                                                                                                                         |

| monitores comerciales de adquisición de signos vitales                                                                                                                                                                                                                                                                                                                                                                     |

| Figura 74. Dinámica de funcionamiento BIOS                                                                                                                                                                                                                                                                                                                                                                                 |

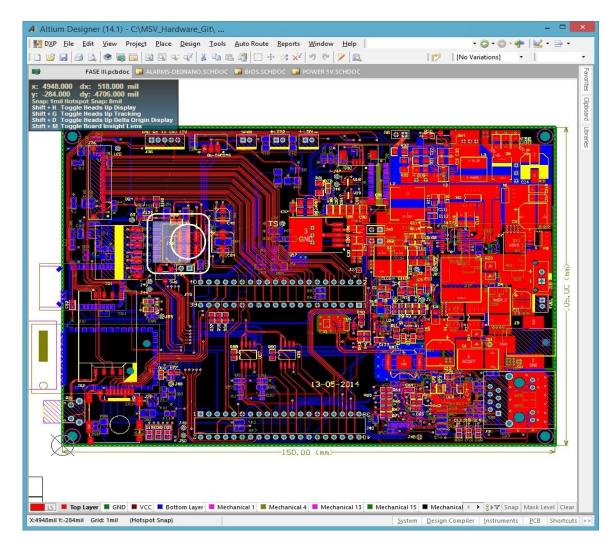

| Figura 75. Espacio de la BIOS sobre el diseño PCB de la tarjeta electrónica principal del sistema de monitorización vital                                                                                                                                                                                                                                                                                                  |

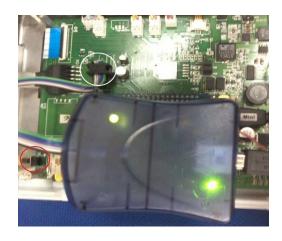

| Figura 76. BIOS en proceso de programación - Conexión adecuada del programador Atmel119                                                                                                                                                                                                                                                                                                                                    |

| Figura 77. BIOS en proceso de programación - Conexión inadecuada del programador Atmel119                                                                                                                                                                                                                                                                                                                                  |

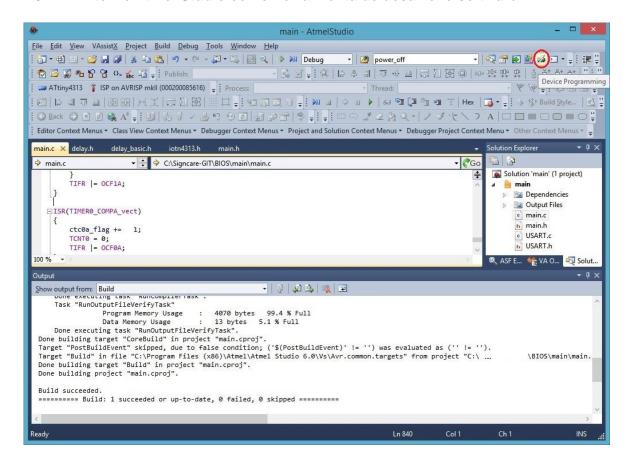

| Figura 78. Entorno Atmel Studio versión 6.0 - Edición del proyecto de nombre "main" 121                                                                                                                                                                                                                                                                                                                                    |

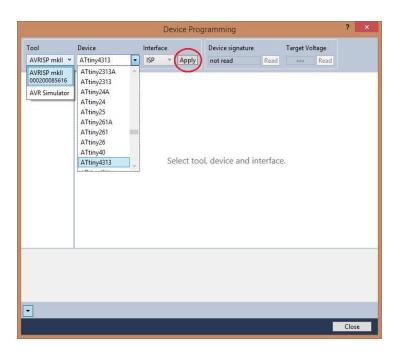

| Figura 79. Aplicando la configuración de programación en el entorno Atmel para con el chip de la BIOS utilizado                                                                                                                                                                                                                                                                                                            |

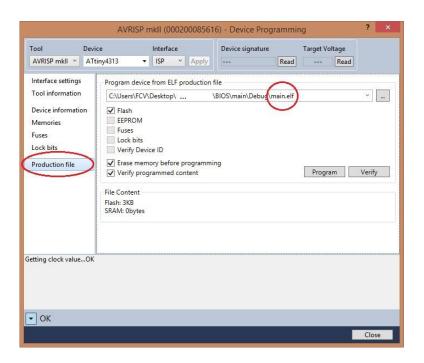

| Figura 80. Verificando el archivo de programación software final "main.elf"                                                                                                                                                                                                                                                                                                                                                |

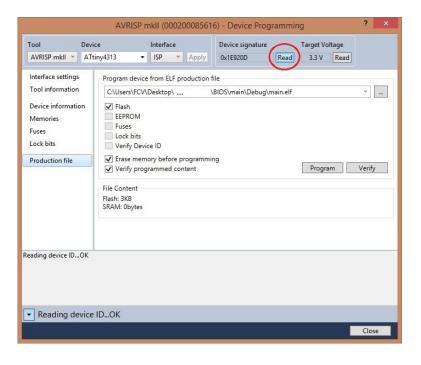

| Figura 81. Verificando las conexiones hardware y disposición del chip físico desde e entorno Atmel.               |

|-------------------------------------------------------------------------------------------------------------------|

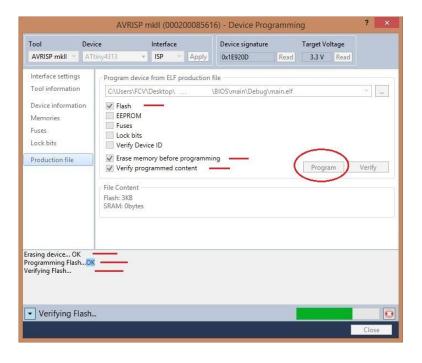

| Figura 82. Ejecutando y verificando la respectiva programación vía programador Atme                               |

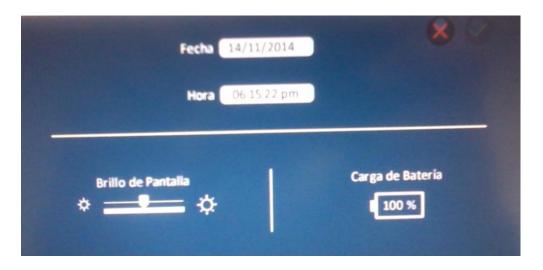

| Figura 83. Información de porcentaje del monitor de signos vitales sobre la interfaz gráfica<br>en el menú varios |

#### **GLOSARIO**

SISTEMA: cualquier conjunto de más de una regla que establecen la lógica de funcionamiento de los entes implicados.

LÓGICA: estructura de funcionamiento de un sistema que puede ser entendida por el pensamiento del ser humando.

ENTORNO/PLATAFORMA: ambiente de trabajo compuesto por una serie de características, normas u opcionalidades propias del mismo, se caracteriza por facilitar la tarea del trabajador en cuanto a visualización rápida e interactiva inmediata, así como interfaz gráfica de usuario en muchas ocasiones.

INTERFAZ: es ese puente o conexión de dos sistemas o mundos, conexión en la cual se relacionan o se crea "interfaz" entre los mismos para lograr un contacto u o dinámica más afín en la visión práctica de su homologo.

GUI: (interfaz gráfica de usuario) es una interfaz o puente de relación entre un sistema ya sea bien informático, embebido entre otros, siendo concedido u o accedido a través de un entorno gráfico siempre, el cual la mayoría de los seres humanos, para este caso, estamos acostumbrados; esto con el fin de hacer esta relación con los diferentes sistemas mucho más intuitiva con el usuario humano final.

EMBEBIDO: referido a aquel sistema computacional que pretende cumplir una respectiva y específica labor a través de la construcción y desarrollo de hardware y o software limitado-especializado para aplicaciones que requieran alta calidad estabilidad y confiabilidad en sus sistemas.

FIRMWARE: conjunto de instrucciones de máquina que describen una serie de acciones de más bajo nivel que la aplicación prestada por un software como tal, ya que son aquellas acciones que le preceden.

BIOS: concepto que abarca una serie de firmware, hardware y lógica de manejo de las diferentes instrucciones de acceso básico hacia un sistema físico específico y desde una perspectiva ligada a factores de interés de este tipo. Se asemeja a una interfaz que facilita la interacción física con los dispositivos de este tipo.

DISEÑO: conjunto de normas, reglas o definiciones que abarcan una herramienta tal y como se conoce y se maneja; el diseño trata de explicar las razones o el porqué de la forma final de los sistemas para así obtener el mayor aprovechamiento de lo que se desea con lo que se tiene dispuesto para el desarrollo de dicha herramienta.

DESARROLLO: proceso continuo de cambios sobre una herramienta con un fin de diseño específico.

IMPLEMENTACIÓN: acción real que abarca un cambio especifico previamente desarrollado sobre las bases de diseño; un desarrollo abarca múltiples implementaciones. PRUEBAS: se incluye en el proceso de desarrollo como una fase extra a la implementación, la cual pretende mejorar o depurar dicho cambio implementado para tener plena seguridad de funcionalidad sobre el mismo.

SECUENCIA: dinámica de funcionamiento que especifica una acción seguida de otra y nunca de forma paralela; de esta manera una secuencia mantiene la premisa de ejecución sobre las bases de la interrupción de eventos y cola de datos, ya que no existe la ejecución de una nueva instrucción mientras una instrucción previa se encuentre en etapa de proceso.

PARALELISMO: característica propia de los sistemas ensamblados en hardware independientemente, en donde un único sistema puede ejecutar varias acciones al mismo tiempo, ya que precisamente se fundamenta en una serie de sub-sistemas independientes, que se encuentran en espacios físicos independientes sobre el mismo sistema final e inclusive pueden o no depender del mismo pero siempre poseen o sostienen una mínima relación de orden para su relación sistemática.

SINCRONISMO: es un proceso que se realiza para establecer cierta característica de secuencialidad u orden en su mayoría a través del dominio del tiempo; esto con el fin de poseer un verdadero control u organización sobre sistemas desorganizados o independientes, como sucede con el paralelismo que soportan algunos de estos sistemas.

HARDWARE: estructura física y palpable de los sistemas.

SOFTWARE: estructura intelectual que se traduce en acciones para el hardware de los sistemas que envuelve; generalmente se asocia con la lógica programable que se compila y descarga en los diferentes dispositivos electrónicos, ya que finalmente son mandatos que se traducen en acciones verificables por el ser humano a través del hardware intrínseco de los sistemas.

ALTERA: compañía fabricante de múltiples dispositivos semiconductores comerciales entre otros servicios y soporte.

ATMEL: compañía fabricante de múltiples dispositivos semiconductores comerciales entre otros servicios y soporte.

MSV: abreviatura de monitor de signos vitales.

SGC: abreviatura de sistema de gestión de la calidad.

SGC: abreviatura de presión arterial no invasiva.

UEE: abreviatura de unidad estratégica empresarial.

VALIDACIÓN: en esta práctica se relaciona con el proceso de verificación funcional, efectiva y carente de fallas del dispositivo MSV bajo desarrollo, con el fin de ofrecer un soporte verídico, fiable y de peso de la funcionalidad del mismo para con el usuario final.

VERIFICACIÓN: proceso que aplica una serie de pruebas sobre pruebas que garanticen siempre la verdad o veracidad de las cosas que se pretenden someter a dicho proceso.

METROLOGÍA: área científica que tiene el objeto de verificar y establecer normas de medición mundialmente aceptadas para con los diferentes sistemas a comparar.

INTERNET: serie de todos los dispositivos electrónicos de red interconectados a través de los diferentes sistemas hardware y lógica software de protocolos de comunicación establecidos para este fin, con el propósito de que exista cierta interacción entre los dispositivos implicados.

PROTOCOLO: serie de secuencias de interacción que permiten una comunicación puente entre las diversas lógicas propias de cada dispositivo independiente; puente de comunicación que hace las veces de traductor universal sobre las bases de un único lenguaje o estándar asociado y aceptado por los dispositivos implicados en el uso del protocolo en cuestión.

RED: se refiere a partes separadas o pequeños grupos de interacción comunicativa entre los diferentes dispositivos electrónicos de red implicados en dicha red. Grupos o sectores de Internet asociados que finalmente conforman a la Internet.

PROGRAMACIÓN: conjunto de descripciones y algoritmos que conforman la lógica de funcionamiento de un sistema. Programar hace referencia a la acción de escribir dicha programación sobre una memoria electrónica destinada para este fin, en la cual se leen los algoritmos por el sistema que procesamiento que después las ejecuta.

LENGUAJE DE PROGRAMACIÓN: descripción literal y o numérica que ofrece una interfaz entre la lógica de instrucciones que entienden los seres humanos, a extensos lenguajes de máquina poco intuitivos, versátiles o molestos para amplios desarrollos que abarcan tiempos limitados.

FPGA: dispositivo semiconductor electrónico caracterizado principalmente por permitir el cambio de su lógica hardware interna a manera de programación descriptiva de la misma, siempre y cuando dicho dispositivo soporte tal lógica descrita. Cada fabricante posee una serie de entornos y herramientas para lograr el desarrollo sobre estos dispositivos al igual que sucede con los microcontroladores y se destaca su flexibilidad en cuanto a lógica física reconfigurable en comparación a otros dispositivos de dinámica netamente software.

MICROCONTROLADOR: dispositivo semiconductor electrónico caracterizado por permitir una serie de programaciones y ejecuciones software sobre un dispositivos de

procesamiento, memorias, periféricos de comunicación externa y otros adicionales, hardware que generalmente no se puede modificar en su estructura como en una FPGA.

DE BAJO NIVEL: referencia a básico, generalmente orientado a instrucciones y lógica de los lenguajes de programación, en donde se describe cada vez más específicamente cada paso, estructura y mínimo detalle posible de tales lenguajes.

DE ALTO NIVEL: referencia a versátil y rápido, generalmente orientado a instrucciones y lógica de los lenguajes de programación, en donde se pretende describir de manera resumida las diferentes instrucciones de funcionamiento de los lenguajes de más bajo nivel, generalmente se caracteriza por incluir compiladores que traducen una instrucción poco detallada, en instrucciones de bajo nivel que entiende la máquina, instrucciones que en la mayoría del tiempo no son evidenciadas por el programador.

EQUIPO DE TRABAJO: reunión de una serie de personas con conocimientos e ideas desordenadas de todo tipo, que pretende orientar las habilidades de sus integrantes a un solo fin, repartición de tareas y las mejores prácticas y metodología de trabajo posible; más en un ambiente de desarrollo de dispositivos electrónicos programables.

VERSIONES: conjunto de implementaciones parciales probadas y verificadas sobre una base medible, las cuales son organizadas y almacenadas para la posteridad con fines exploratorios que devienen del error humano y la carencia de perfección en los procesos.

SOPC BUILDER: entorno de desarrollo hardware basado en la unión de modularidad hardware prediseñada, con fines a la implementación de sistemas más confiables y rápidos.

QSYS: entorno de desarrollo póstumo al entorno SOPC BUILDER, que plantea una perspectiva más clara para el desarrollador, con mayores prestaciones en cuanto a la integración de las nuevas tecnologías y disminución de errores o BUGS de su entorno predecesor.

BUG: traduce "bicho o insecto" en ingles conocido por uso común en entornos de desarrollo de programación y se refiere a esa falla o afectación de un sistema, al punto de afectar su funcionamiento por completo; estos fallos muchas veces se evitan realizando procedimientos fuera de lo estándar y otras veces no es tan sencillo y limitan el trabajo de quien los enfrenta.

CULOMBIO: unidad de carga que se proporciona como referenciación de los elementos que almacenan energía eléctrica, esta es una medida derivada de la capacidad de carga de un electrón v sus unidades son "A\*s" (Amperio segundo).

#### **RESUMEN**

TITULO: PRÁCTICA EMPRESARIAL EN LA UEE BIOINGENIERÍA DE LA

FUNDACIÓN CARDIOVASCULAR DE COLOMBIA: DISEÑO, OPTIMIZACIÓN E IMPLEMENTACIÓN DEL SISTEMA SOFTWARE-HARDWARE E INTERFAZ GRAFICA DE INTERACCION CON EL

USUARIO DE UN DISPOSITIVO DE MONITORIZACION VITAL

AUTOR: JOSE MANUEL VELANDIA ROJAS

FACULTAD: FACULTAD DE INGENIERÍA ELECTRÓNICA

DIRECTOR: MSc. CLAUDIA LEONOR RUEDA GUZMÁN

Esta práctica fundamenta su estudio e investigación en el campo de los sistemas embebidos más modernos, de alta capacidad y bajo costo, que pueden encontrarse hoy en día en el desarrollo de nuevas tecnologías, además de software embebido y dispositivos alternos.

El proyecto sobre el cual se fundamenta este trabajo, se encuentra bajo desarrollo y producción en las instalaciones de la Fundación Cardiovascular de Colombia y abarca la creación de un monitor de signos vitales (MSV) para su uso interno, así como venta nacional e internacional del equipo resultante.

Se ha hecho necesario retomar estudios sobre dispositivos de lógica digital programable (FPGA), sistemas embebidos, electrónica de potencia, sincronización de señales, concepto de interfaz gráfica de usuario en base a programación básica, programación referida a objetos y una corta etapa de diseño de PCBs sobre el software Altium Designer para el entendimiento base de la conectividad entre tarjetas e identificación de problemas de tipo físico que tuvieron cabida en el proyecto.

La idea del proyecto se centra en una tarjeta de adquisición de signos vitales siendo reconocida por una lógica de recepción y configuración en la FPGA que procesa las distintas señales sobre un dispositivo interactivo compuesto por una pantalla táctil resistiva en la cual se presentan las distintas señales adquiridas y las distintas configuraciones a las que puede acceder el usuario a través de una interfaz gráfica de usuario GUI. Lo anterior abarca una serie de lógica paralela para la adquisición de los datos, señales de video propias en RGB, montaje de procesadores embebidos partiendo de lógica hardware programable de propiedad intelectual de la compañía Altera (Versatilidad de aplicación software), entre otros agregados de portabilidad como lo es el control de carga de la batería y otros más externos de comunicación vía Internet y redes 3G que poco se mencionan para esta práctica.

#### PALABRAS CLAVES:

GUI, PROGRAMACIÓN, OBJETOS, ADQUISICIÓN, MONITOR, SIGNOS VITALES, DISEÑO, DESARROLLO, FPGA, DESCRIPCIÓN HARDWARE.

VoBo DIRECTOR DE TRABAJO DE GRADO

#### **ABSTRACT**

TITLE: BIOENGINEERING STRATEGIC ENTERPRISE UNIT OF THE

CARDIOVASCULAR FOUNDATION OF COLOMBIA - GRADUATION PRACTICE: DESIGN, OPTIMIZATION AND IMPLEMENTATION OF SOFTWARE-HARDWARE SYSTEM FOR GRAPHIC USER INTERFACE

**FACILITIE OF A DEVICE FOR MONITORING VITAL**

AUTHOR: JOSE MANUEL VELANDIA ROJAS

FACULTY: ELECTRONIC ENGINEERING FACULTY

DIRECTOR: MSc. CLAUDIA LEONOR RUEDA GUZMÁN

This practice based his study and research on embedded systems field always looking of the most modern, high capacity and low cost devices, which can be found nowadays on the go of new technologies development, in addition to embedded software and alternative devices.

The project on which this paper is based, is under development and production inside the Cardiovascular Foundation of Colombia place and covers the creation of a vital signs monitor (MSV) for use on the organization plant itself, as well as national and international sale of the resulting medical equipment.

It was necessary to resume studies about digital programmable logic devices (FPGA), embedded systems, power electronics, signal synchronization, concept of graphical user interface based on object-referenced and basic software programming, finally a short stage of PCB design on Altium designer software for database connectivity between boards and physical trouble identification that took place in the draft understanding.

The idea of the project focuses on an acquiring vital signs board being recognized by a receptional and configurational hardware logic on the FPGA, which processes the various signals on an interactive device comprising by a resistive touch screen in which the different signals acquired and different configurations for user input can be accessed through a graphical user interface GUI. This comprises a series of parallel logic for data acquisition, own video signals in RGB format, installation of embedded processors over programmable hardware logic from Altera's company intellectual properties (Versatility of software application), among other aggregates of portability as it is controlling battery charge and others more external about communication via Internet and 3G networks which are little mentioned for this practice.

#### **KEYWORDS:**

GUI, PROGRAMMING, OBJECTS, ACQUISITION, MONITOR, VITAL SIGNS, DESIGN, DEVELOPMENT, FPGA, HARDWARE DESCRIPTION.

| VoBo T | HESIS I | DIRECT | OR |  |  |

|--------|---------|--------|----|--|--|

## INTRODUCCIÓN

La UEE (Unidad Estratégica Empresarial) Bioingeniería, hace parte de la FCV (Fundación Cardiovascular de Colombia) como la sub-empresa dedicada a la elaboración, producción, calibración, validación, prestación de servicios de salud, soporte técnico, adecuación de dispositivos médicos, así como el diseño y desarrollo de los mismos; esta labor tiene como fin no solo aportar en el desarrollo biomédico interno en beneficio del hospital de la organización, sino lograr un desarrollo de impacto tecnológico en la región, como ya se puede apreciar a través de la construcción actual del hospital internacional de la FCV y su amplia gama de servicios a la mano de la comunidad.

Uno de los objetivos más importantes de la organización siempre ha sido obtener reconocimiento y validación ante las diversas normas y estándares nacionales e internacionales, mientras que cada colaborador pueda aportar con calidad al usuario final a través de sus conocimientos profesionales de la mano con las políticas que se manejan internamente. Desde esta perspectiva el área de bioingeniería pretende alcanzar una visión en la que no solo a través de prestación de servicios de salud la organización puede verse beneficiada y reconocida, sino también en la medida que las capacidades que poseen los profesionales en la región puedan aportar para ser reconocidos como un centro tecnológico biomédico cada vez más especializado y profesional, desarrollar tecnologías propias que pudiesen ayudar a miles de personas, mientras los nuevos desarrollos se abren paso para competir en el mercado contra los bajos precios de países netamente productores, esto a través de las nuevas tecnologías que se implementan en el área; a este objetivo principal le apunta el proyecto del monitor de signos vitales y su interfaz gráfica de usuario que se plantea en esta práctica, un proyecto innovador que busca reconocimiento del área para sacar adelante la UEE de bioingeniería y ser tenidos en cuenta más profesionalmente y así de la mano con el apoyo de la organización, proponer mejores proyectos de mayor complejidad y de mayor calidad.

En la actualidad se posee un prototipo funcional del MSV e inclusive una pequeña producción de prueba, de la cual se pretenden abarcar todas las fallas, cosas que se pasaron por alto y en resumen reunir toda la información necesaria del equipo, para hacerlo realmente comercial y depurar por completo sus funcionalidades.

A lo largo de este tiempo, que inclusive supera el periodo de esta práctica empresarial, se han venido haciendo múltiples investigaciones, inversión de tiempo en situaciones no planeadas, autogestión del nuevo conocimiento, cursos externos y demás; también se han afrontado múltiples problemas proyectados en esta práctica de grado, tiempo que ha sido de gran ayuda para encontrar tanto debilidades que debe superar cualquier profesional, como fortalezas que se deben seguir cosechando para así transmitir dicho conocimiento en pro del desafío que supone este inmenso proyecto en el que se han invertido tantos esfuerzos de un equipo de trabajo comprometido.

En este punto del desarrollo actual del monitor de signos vitales, se tiene una sólida base hardware y mejoras de todo tipo en cuanto a estabilidad del sistema, nuevos desarrollos funcionales y más rediseños con pruebas e implementaciones finales que pretenden mejorar el rendimiento actual del monitor en cuestión. Es entonces momento para finiquitar algunos desarrollos y generar algunos instructivos al conocimiento referente a la nueva herramienta de diseño hardware "Qsys", para luego ingresar en el campo de desarrollo software, necesario para abordar muchas de las tareas funcionales del equipo, ya que el mundo hardware no se encuentra muy acoplado para todos los procesamientos que se pretenden realizar, se hace importante sacar ventaja también de la secuencialidad que proporciona la interacción software con el equipo de monitorización.

En la primera etapa del proyecto se abordaron temas teóricos referidos a la utilización de sistemas funcionales y comprensión física del montaje básico del monitor, temas teóricos respecto al desarrollo software que hace parte de la segunda etapa de esta práctica y uso de sistemas hardware, diseño y desarrollo sobre FPGAs y embebidos de todo tipo.

Hubo un espacio bastante amplio para la familiarización con el MSV en cuestión y los diversos entornos de desarrollo, así como investigación y referenciación con sistemas comerciales de monitoreo existentes en el hospital de la organización (ICF), tiempo mucho mayor al que aborda esta práctica, pero pudo ser administrado en su momento; esta aclaración se realiza para dar una idea al lector acerca de la importancia de la investigación y el planteamiento de los requerimientos.

Una vez adquiridos los conocimientos y haber absorbido el desarrollo hardware, la segunda etapa del proyecto se centró en adquirir esa habilidad de software que permitirá modificación de todo tipo en la supresión de errores de interfaz entre otros, errores tanto complejos como evidentes saldrán a la luz de la mano con el trabajo del área de validación y metrología de bioingeniería, quienes serán los encargados de poner a prueba el equipo y de ver aquello que genere no conformidades o fallas críticas al sistema del equipo médico.

Este último ha sido un proceso bastante largo debido a la inmensidad del código y adentra los desarrollos en adquirir ese nivel requerido de experticia desde el inicio de la práctica, lo cual permite abordar la responsabilidad de las mejoras y fallas que el equipo vaya presentando a lo largo de este proceso.

## Objetivo general

Diseñar, optimizar, e implementar la estructura del sistema software-hardware básico para la interfaz gráfica de usuario, de un dispositivo de monitorización vital, utilizando conocimientos teóricos y prácticos de tipo programático, digital y manejo de datos, en la línea de desarrollo tecnológico de sistemas embebidos. Generación y corrección de librerías en código C/C++.

## Objetivos específicos

- Implementar y describir el sistema modular software-hardware que guiara las tareas del dispositivo de monitorización, sistema operativo y entornos de desarrollo innovadores aun no utilizados para este tipo de tarjetas de desarrollo en base a los conocimientos del estudiante e investigaciones iniciales requeridas.

- Optimizar el sistema para reducir las posibles fallas en módulos de video existentes, implementar señales de video más estables que eviten limitaciones de frecuencia y ruido interno.

- Diseñar e implementar nuevos dispositivos de comunicación interna más eficientes.

- Integrar los diferentes periféricos de video, comunicación local, envió de señales al exterior del procesamiento software por medio del softcore Nios II.

- Rediseñar y programar el software embebido en el procesador principal, gestionar los gráficos e interfaz de ventanas del sistema actual, en un entorno optimizado de mayor resolución y solucionando problemas de estabilidad.

#### Actividades

- Estudiar las diversas interfaces de monitores ya desarrollados para estructuración e implementación en el monitor De signos vitales.

- Se hace imprescindible estudiar la estructura de monitores actuales como guía en el proceso de creación del nuevo dispositivo de monitorización en pro de agilizar el proceso de diseño y desarrollo del mismo.

- Investigar métodos de descripción hardware y software avanzados, facilidades de uso entre sistemas operativos y demás pautas que definirán el desarrollo de ahora en adelante.

- Se deben retomar conocimientos base para aplicar diseños avanzados que generen mayor desempeño, robustez, sincronía y confianza al momento de ser implementados e integrados con otros diseños; se deben definir las herramientas (entornos, códigos, sistemas operativos, interfaces físicas) que se van a utilizar desde un inicio, evitando cambios inesperados que afecten tanto el desempeño del sistema que puedan a su vez generar demoras a los tiempos establecidos para el desarrollo del sistema de monitorización.

Diseño y descripción de las bases hardware embebidas para el dispositivo en cuestión, implementación, rediseños y pruebas finales.

Esta etapa abarca pruebas de cada módulo hardware por separado y de ser necesario, implementación funcional con los demás módulos, detección de fallas, optimización y rediseño de lógicas actuales, creación de nuevos módulos, e integración interactiva con el sistema gráfico y adquisitivo global.

Implementación software en el procesador Nios II, generalidades, detalles de funcionamiento y guías de uso en el entorno previamente definido.

Esta etapa incluye el uso del hardware existente hasta el momento, siendo administrado por software de forma básica por el procesador embebido en las diferentes tareas que deben ser implementadas en tiempo real.

Diseño de la interfaz gráfica básica aplicada a través del uso de librerías software orientadas a objetos. Manejo de "sprites" en memorias, carga no volátil de las distintas descripciones.

Esta etapa incluye el desarrollo software, uso de librerías y convivencias de códigos C y C++, administración de copiados masivos de memoria para generar una interfaz relativamente fluida intuitiva e interactiva con el usuario, además de coherente respecto los diferentes módulos de aplicación hardware, controladores, drivers, táctiles de pantalla y demás capas físicas que componen el dispositivo, pruebas e implementaciones experimentales, verificaciones de funcionamiento, rediseños finales y entrega final de interactividad usuario-interfaz.

# Cronograma de actividades

|                                                                                                                                                                                                                  |   | Semana. |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|

| Actividades.                                                                                                                                                                                                     | 1 | 2       | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| Estudiar el monitor previo.                                                                                                                                                                                      |   |         |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |

| Estudiar métodos de descripción avanzados y definir las herramientas a utilizar a lo largo del desarrollo.                                                                                                       |   |         |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |

| Diseño y descripción<br>de las bases hardware<br>embebidas para el<br>dispositivo de<br>monitorización, sobre<br>una específica tarjeta<br>de desarrollo basada<br>en tecnología FPGA.                           |   |         |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |

| Implementación<br>software en el<br>procesador Nios II,<br>manejo del entorno<br>previamente definido.                                                                                                           |   |         |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |

| Diseño de la interfaz<br>gráfica básica<br>interactiva con el<br>usuario, uso de<br>librerías software<br>orientadas a objetos,<br>manejo de memoria y<br>carga no volátil de las<br>distintas<br>descripciones. |   |         |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |

#### 1. ESTUDIO INICIAL Y METODOLOGIA DE TRABAJO

Antes de iniciar a realizar cualquier tipo de desarrollo respecto al monitor de signos vitales referido a esta práctica, se hace un previo estudio su estructura, concepto, bases, planeación y lo más importante, su electrónica y funcionamiento en forma global, esto con el fin de evitar el choque de información que suele suceder cuando se realiza la organización de la información concerniente, después surge la necesidad de ingresar en un nuevo tema y dado a la falta de conocimiento del mismo, se terminan extraviando los conceptos, se cometen errores, se pierde tiempo y se termina necesitando del apoyo y la información que puedan facilitar los compañeros de trabajo en momentos poco oportunos; lo anterior podría abarcar bastante tiempo y dedicación poco disponibles en momentos adecuados, orillando al estudiante a ser un mal autodidacta y a atrasarse en su cronograma, sin embargo son estrategias de aprendizaje que se pretenden evitar interviniendo de manera ordenada y oportuna a cada labor que se vaya presentando, todo en función de aprovechar mejor los espacios, en la medida que estas pautas definen la metodología de trabajo.

En la investigación que se realizó de mano de los ingenieros electrónicos Sherneyko Plata Rangel y Jose Pablo Pinilla Gómez, desarrolladores actuales del monitor en cuestión, se extrajo un vasto conocimiento de todo lo que refiere al sistema electrónico y la tarjeta de adquisición, diseños completamente propios de todo el sistema embebido, tarjetas electrónicas, programación hardware en FPGAs, software embebido de interfaz gráfica de usuario (GUI), utilización de licencias de software en el uso de propiedades intelectuales de la compañía Altera, manejo muy básico del software Altium Designer para diseños de PCB en el proceso de la recolección de la información necesaria para incursionar en los diferentes sistemas físicos, derechos de uso en cuanto a las librerías de uC/OS II como sistema operativo en la tarea de compilación de la plataforma embebida y demás material que se ira absorbiendo con el paso de la lectura.

## 1.1 COMPRESIÓN DE LOS SISTEMAS PREVIAMENTE DESARROLLADOS

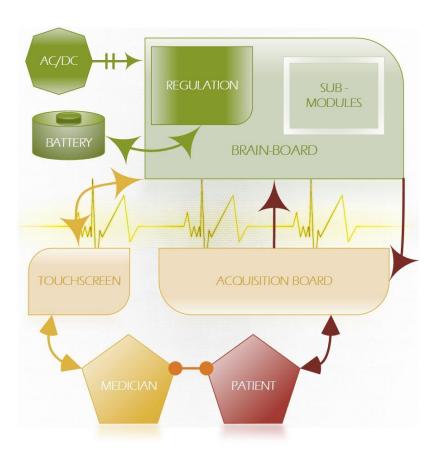

Entrando un poco más en materia acerca de los sistemas que componen a detalle el monitor, se inicia con el avistamiento físico del mismo, del cual se extraen los dispositivos clave más externos y se determina el funcionamiento base a gran escala del equipo, extracción de conocimiento que pretende resolver en la Figura 1 que representa la composición del monitor en cuestión y su interacción con el medio, así se tiene una idea más clara de lo que se posee, función y lo que se pretende hacer con esto.

#### 1.1.1 Extracción de la dinámica base.

Figura 1. Sistemas externos del MSV e interacción con el mundo físico.

Como se puede apreciar en la Figura 1, el proyecto del monitor de signos vitales (MSV) trata de abarcar el concepto de una tarjeta de adquisición de signos vitales siendo montada o ensamblada en una tarjeta electrónica para cumplir múltiples labores de procesamiento (Mainboard); un sistema gráfico de pantalla táctil pretende que el usuario (Personal asistencial médico) pueda acceder a todas las funcionalidades y opcionalidades ofrecidas por dicha tarjeta de adquisición, que en esencia, pretende trabajar sobre un determinado tipo de pacientes a través de los conocimientos profesionales que pueda aportar dicho personal asistencial al sistema de monitorización vital en general; cabe aclarar que la tarjeta de adquisición de signos vitales es un tipo de tarjeta completamente comercial que ha sido probada con ciertos estándares médicos especificados en su respectiva hoja de datos (la cual es proporcionada por su fabricante) y por ende no deviene ningún desarrollo funcional de la misma por parte de los ingenieros, sin embargo se debe diseñar el sistema de comunicación con la misma y ser muy cuidadoso con ciertos aspectos para con el sistema embebido global y la integridad del usuario final (médico - paciente).

Este concepto viene acompañado por ciertos agregados desde el punto de vista electrónico y programático que poseen la mayoría de monitores comerciales, en los que se pretende dar al usuario cierto nivel de estabilidad y portabilidad con el uso de baterías, sub-módulos de comunicación, así como realimentación visual y auditiva, registro de datos en tarjeta de memoria SD que aporten al seguimiento de tendencia fisiológica médica del paciente y resolución de problemas legales que puedan surgir respecto a fallas propias del equipo, problemas de configuraciones erróneas (factor humano), menús de orientación para el usuario final y otros extras que ayudan a manipular el monitor de manera más precisa y confiable; lo anterior a través de la interacción organizada que proporciona la interfaz gráfica de usuario (GUI) del dispositivo.

Otro punto importante al momento de diseñar la interacción gráfica que se da a través de la pantalla táctil, es evitar el índice de desorganización que pueda reflejarse en el usuario debido a dicha interfaz y así sin importar la complejidad que pueda abarcar el monitor, el usuario final siempre suponga un mínimo de ajuste necesario al momento de su uso en pacientes y se refleje la espontaneidad de manejo del dispositivo, este es un factor crucial para que el usuario desee adquirir el producto, es un índice de organización de los elementos que debe ser analizado a detalle y que pocos monitores de signos vitales en el mercado poseen, ya que los menús se tornan algo complicados si no se tiene la suficiente experticia en su manejo, como ya se ha evidenciado por los distintos colaboradores del área, el estudiante, e inclusive las opiniones y experiencias del mismo personal asistencial, lo cual supone uno de los más grandes retos de este proyecto, ya que plantear este concepto sobre un medio de programación embebido tan poco explorado es claramente incierto.

En este punto ya se tiene la idea base y el concepto respecto al cual se desarrollará un monitor de signos vitales, sin embargo hay que ser un poco más específico respecto al desarrollo electrónico se refiere, ya que aunque se posee un concepto y unos requerimientos que se reparten en funciones para con el equipo de trabajo, no se tiene mayor idea del tema específico en cuanto a descripciones del sistema y dispositivos electrónicos a usar; es por ello que hay que darle paso al estudio del monitor en cuanto a los sistemas electrónicos específicos.

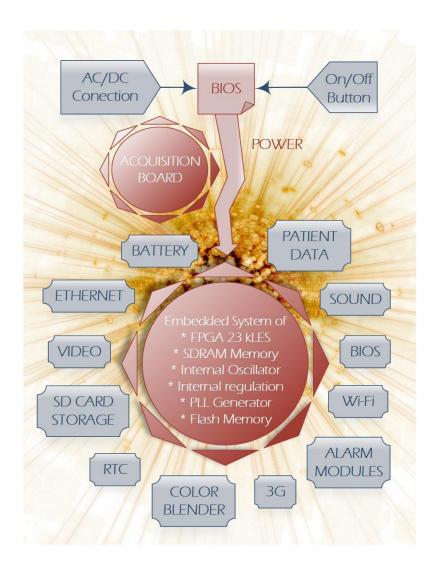

En la Figura 1 se pudo evidenciar la existencia de una tarjeta cerebro (Mainboard) que alberga una serie de sub-módulos y regulación de alimentación para el equipo en general, sin embargo quien lleva el verdadero control de esta serie de elementos como sub-módulos, la sincronización para el video de pantalla, la adquisición de datos, comunicación interna y externa, parte del control de carga de la batería entre otros, es el control referido al procesamiento que realiza una FPGA sobre casi todos los periféricos físicos base explicados con anterioridad y muchos otros que se verán a través del desarrollo de esta práctica. Para entender de forma más clara la función de dicho procesamiento se plantea la Figura 2.

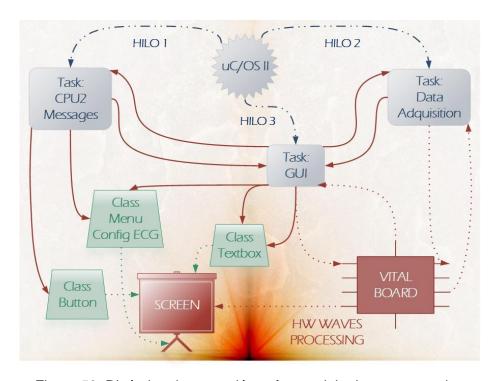

Figura 2. Esquema de correlación de las tareas, respecto a la tarjeta de procesamiento principal.

Como se puede apreciar en la Figura 2, la FPGA no actúa por completo sola, ya que el sol representativo de en medio del esquema, plantea toda una tarjeta de desarrollo dotada de múltiples memorias, oscilador y regulación propia embebida además de su respectiva FPGA de cierta capacidad lógica; todos estos dispositivos embebidos dentro de la tarjeta, son un puente crucial para evitar gasto de lógica interna, evasión del ruido dado a la conexión interna de la memoria volátil de alta frecuencia (SDRAM), generadores de oscilación estables, memoria no volátil prefabricada y conectada internamente, quienes a su vez evitan cierto gasto de pines libres que requerirán los demás dispositivos externos con los que se tendrá que comunicarse dicho módulo de procesamiento principal (FPGA); interacción con el exterior ejemplificada a través de las puntas del sol de la Figura 2.

El funcionamiento normal del sistema se basa en una secuencia de tareas, en donde la FPGA al igual que la tarjeta externa de adquisición de signos vitales, serán alimentadas y

encenderán gracias a la acción ofrecida por un microchip que cumple la función de bajo nivel conocida como BIOS del sistema, encargada de la carga inicial y procesos base de todo sistema embebido, esta a su vez otorgará control sobre la alimentación y el encendido del equipo una vez este sea energizado correctamente, es entonces donde la FPGA podrá tomar el control de múltiples periféricos y módulos externos a través de sus múltiples pines de entrada, salida y de bi-dirección, todo esto mientras su descripción programática sea correctamente cargada a la misma a través de una serie de memorias flash no volátiles previamente tratadas por los ingenieros electrónicos y el estudiante en práctica; por otra parte la información no volátil será volcada a la memoria volátil del sistema conocida como SDRAM, quien gestionará un procesamiento mucho más rápido y funcional referente al desarrollo de programación software, gestión propia de los procesadores softcore descritos en hardware (propiedad intelectual de la compañía Altera) quienes junto a otros módulos de video dentro de la misma FPGA y memorias, logran una interfaz gráfica perfectamente funcional, fluida y en armonía con todos los periféricos y descripciones hardware que componen el sistema.

Cabe aclarar que el microchip que fue designado a ocupar su función como BIOS del sistema, es un chip de la compañía Atmel perfectamente comercial y por ende también conlleva cierto desarrollo en programación software, esta programación es llamada a funcionamiento a través de una pequeña memoria no volátil construida internamente dentro de este chip, así que no se requirió de otra memoria externa para cumplir con el objetivo de plantear una BIOS completamente funcional; sin embargo se aclara que las funcionalidades y el desarrollo en este tipo de dispositivos conllevan un vasto estudio de sus respectivas hojas del datos, las cuales son proporcionadas por el fabricante y se analizaron en el transcurso de la práctica, esto con el fin de corregir problemas, arreglar y agregar funcionalidades que surgieron en medio del desarrollo de todo el equipo médico por la generación de nuevos requerimientos emergentes de los cuales no se está exento.

## 1.1.2 Uso de propiedades intelectuales (IP).

Este es el punto en donde los mundos hardware y software se encuentran para complementar sus faltas y hacer un sistema completo con todas las ventajas disponibles y las desventajas que vayan surgiendo de las cuales se puede aprender a aplicar en proyectos futuros; igualmente poner en conocimiento la flexibilidad que se evidencia al trabajar con dispositivos de la compañía Altera, ya que en cuanto a sus propiedades intelectuales y desarrollos propios se refiere, siempre existe un uso verificable en comparación a otras compañías, las cuales obligan al usuario a depender de una licencia para cualquier mínima prueba de las funcionalidades de sus desarrollos intelectuales; en este aspecto la compañía Altera no se cierra y permite el uso restringido pero funcional de sus sistemas, lo cual resulto ser bastante útil en situaciones que conllevan gastos financieros no contemplados, liberando así cierta presión y encadenamiento a licencias, más aún en sistemas que atraviesan por sus desarrollos iniciales sin una garantía total de funcionamiento, como lo evidenciaría cualquier desarrollo de sistemas embebidos.

#### 1.1.3 Cuestionamientos iniciales.

Ya se tiene el objetivo, ya se tiene el sistema, ya se tienen las funcionalidades y ya se tiene una base más clara de la situación del desarrollo electrónico; sin embargo es el momento para preguntar, ¿Porque FPGA? y entrar en contexto a una corta etapa de investigación en cuanto a ventajas y desventajas, capacidades y necesidades que posee el proyecto, con el fin de tener aún más claro que se puede y que no se puede hacer con los recursos predispuestos; esto se da ante la necesidad de evitar problemas que surgen con los nuevos requerimientos, en donde un nuevo planteamiento que abarca un respectivo ajuste genera compromisos que se son imposibles de cumplir ya sea por los recursos, falta de conocimientos actuales o por la presión que generan decisiones apresuradas en términos de responsabilidad con las labores asignadas sobre el equipo de trabajo, acción que se traducirá en una cola de labores inconclusas que afectan la fluidez del proyecto y la calidad final vista por los directivos, que desde el desarrollo es evidenciada por todo el equipo de trabajo y el producto en general.

De la investigación que se plantea sobre el dispositivo de procesamiento principal se ajustan las siguientes dudas sencillas pero claves para el entendimiento del mismo, junto con otros conceptos que deben ser asimilados desde un comienzo.

- ¿Qué es una FPGA?

- ¿Para qué se utiliza una FPGA?

- ¿Cómo se logra el desarrollo en una FPGA?

- ¿Cuáles son los aspectos que destacan el desarrollo sobre una FPGA?

- ¿Cómo ha sido la evolución de las FPGA?

- ¿A qué se refiere un sistema embebido?

- ¿Cómo se aplica el concepto de sistemas embebido a este proyecto?

- ¿Cuáles son las ventajas y desventajas de un sistema embebido?

- ¿Desventajas de los sistemas embebidos?

## 1.2 INVESTIGACIÓN Y FAMILIARIZACIÓN CON EL ÁREA DE TRABAJO

Existe una etapa intermedia que plantea definir los requerimientos que debe tener el monitor para asemejar su funcionamiento comercial, dado que en su momento no se tuvieron en cuenta algunos factores importantes; este trabajo ayuda a generar ideas en la creación, diseño y modificación de los sistemas que se abarcaran más adelante, en función de distribuir las tareas necesarias para el equipo de trabajo en cuestión.

## 1.2.1 Problemas que impulsaron la investigación.

En el proceso de definición de los requerimientos del proyecto existieron situaciones que no se analizaron muy claramente, no se definieron como debió en su momento o sencillamente no se pensaba que pudiesen afectar al sistema, sin embargo se evidenció como a puertas de depurar el proyecto, ese bajo nivel de planeación que en cierto punto afectaron los recursos, el tiempo y calidad de los sistemas. Establecer una planeación clara para un proyecto, es un proceso tan fundamental como en el desarrollo exitoso del mismo y toda esta problemática orillan al equipo de trabajo a redefinir ciertos requerimientos en base a un proceso de investigación-definición-solución.

Dado que el MSV de la FCV pretende a futuro ser un sistema igualmente competitivocomercial, la idea de comparar el monitor en cuestión con los equipos de la clínica, surge como una rápida salida que pretende abordar con precisión cada detalle fallido, indefinido o faltante en el equipo; de esta manera, una de las tareas previamente asignadas al estudiante se cumple a cabalidad y se ve reflejada en las múltiples visitas comparativas realizadas en la clínica, informes de registro de los datos investigados, así como pruebas visuales y auditivas ejecutadas en su momento para el sistema de gestión de la calidad (SGC) de la organización.

## 1.2.2 Evidencia de la investigación.

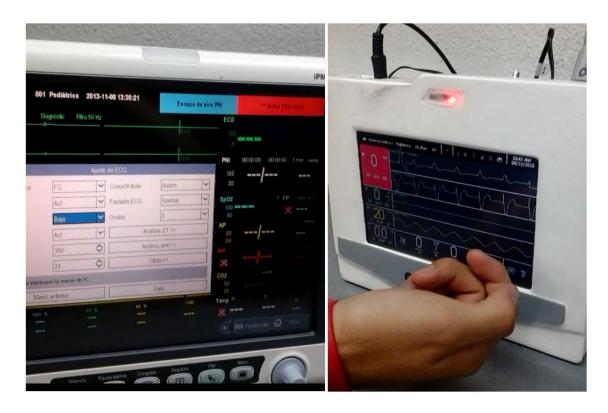

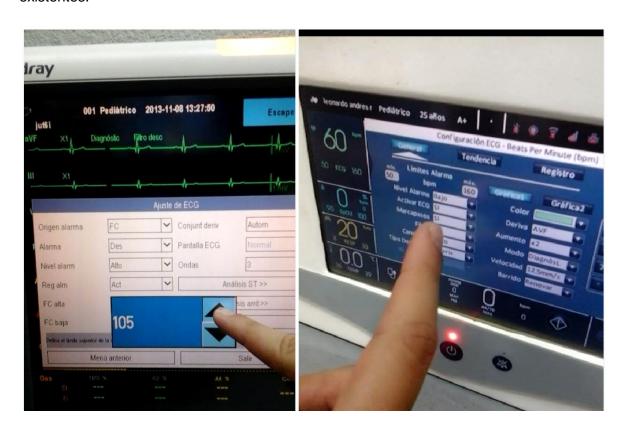

En las imágenes comparativas, se evidencia al monitor comercial en la parte izquierda y al monitor FCV (prototipo funcional) en la parte derecha más su respectiva descripción.

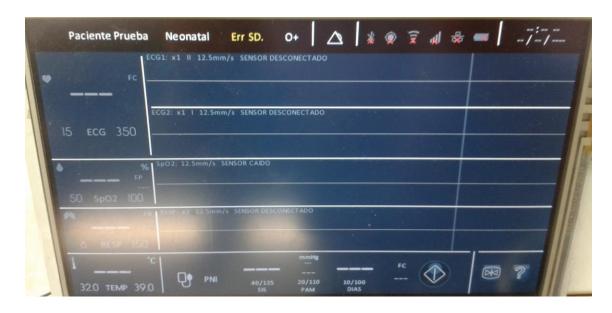

Figura 3. Pruebas en video - Verificación de alarmas y representación de valores estáticos en monitor comercial.

En la prueba de la Figura 3, se pudo verificar como las alarmas poseían un nivel determinado el cual no cambiaba su configuración por parte del usuario a menos que el paciente entrara en estado crítico, lo cual se tenía implementado pero no de la manera que el monitor comercial lo proponía. También se evidenció la representación escrita de alarmas técnicas (como lo son las caídas de sensor o fugas de PANI), lo cual no poseía el equipo de desarrollo en absoluto, por otro lado la representación gráfica de los valores estáticos en reposo, siempre se establecía a través de líneas horizontales de la forma "---" para el monitor comercial y no a través de números cero (0) como se refleja en el monitor de desarrollo; de esta manera se pudieron recoger varias percepciones importantes en el diseño y desarrollo de los cambios funcionales y de interfaz pertinentes, evitando siempre que los nuevos cambios tuviesen una intervención negativa sobre los desarrollo existentes.

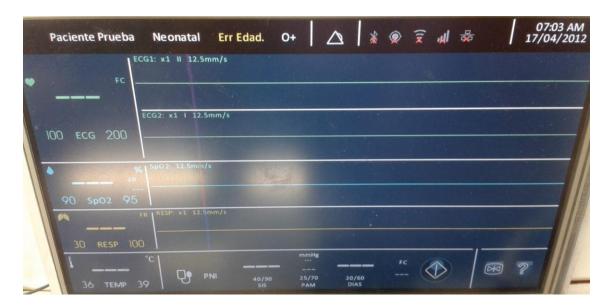

Figura 4. Pruebas en video - Verificación de límites de alarmas y modos gráficos de las ondas vitales.

En la representación de la Figura 4, se pudo verificar cada límite de alarma y configuración predeterminada que tuviese el monitor comercial con respecto a los ajustes que conlleva el cambio de tipo de paciente, lo cual pudo ser validado junto a la información referida en los respectivos manuales disponibles de estos equipos comerciales, esto en comparación a la opcionalidad de configuración en cuanto a límites que ofrecía en monitor de la FCV y el correcto ajuste de los mismos; por otro lado también se verificaron los diferentes modos de velocidad, barrido, amplitud y modo de onda que pudiese existir para cada parámetro, en donde cada cual podía informar de su situación a

través de un mensaje superior al parámetro concerniente, cosa que aunque ya estaba implementada en el monitor local, existía una escasez de información poco funcional para el proyecto, lo que conlleva al aumento de ciertos mensajes informativos y optimización de los espacios a través de técnicas de pestañeo visual para los campos necesarios.

Otras observaciones y optimizaciones respecto a datos de alarma y comportamiento de los mensajes informativos distribuidos por toda la pantalla se llevaron a cabo a través de las múltiples reuniones con el equipo de trabajo.

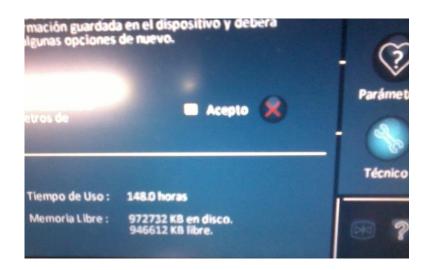

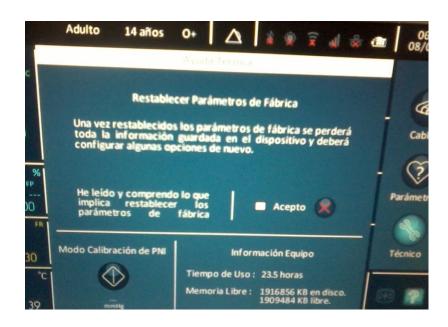

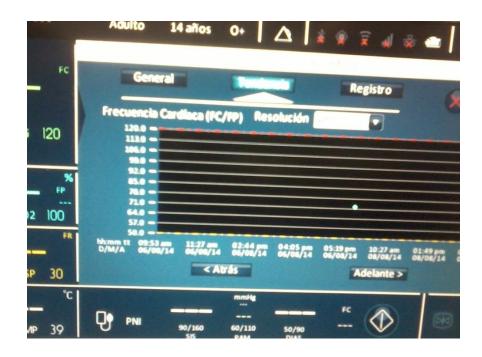

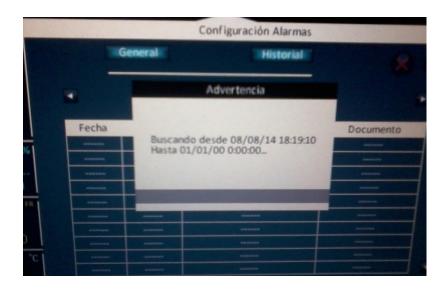

Figura 5. Pruebas en video - Verificación de sonidos, pausa de alarmas, iconografía de interfaz e iconografía externa.